Dear support,

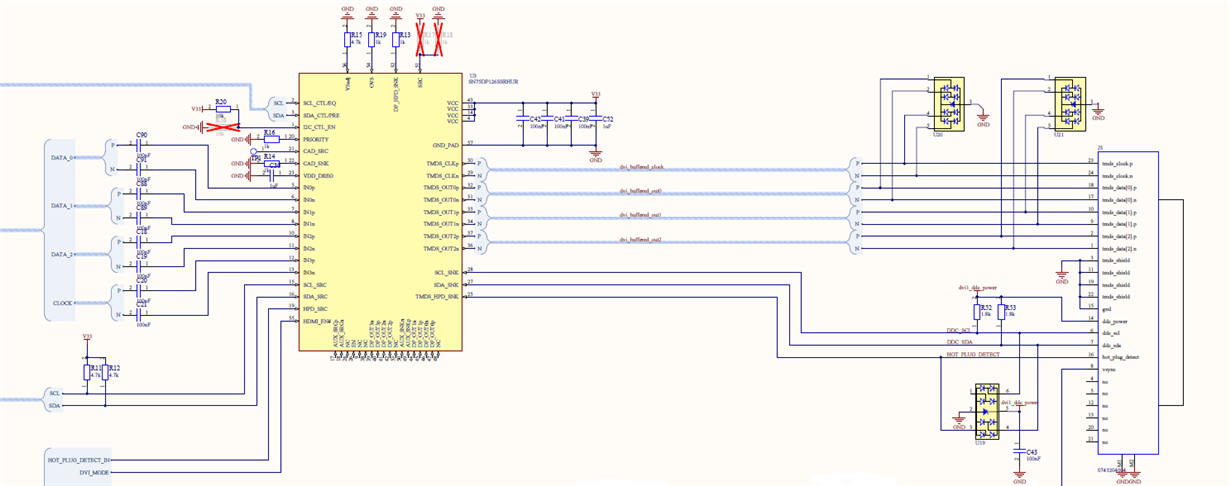

The SN75DP126 device should provides the status of the Hot Plug Detect sink (HPD_SNK input) from a monitor to the digital controller (HPD_SRC output).

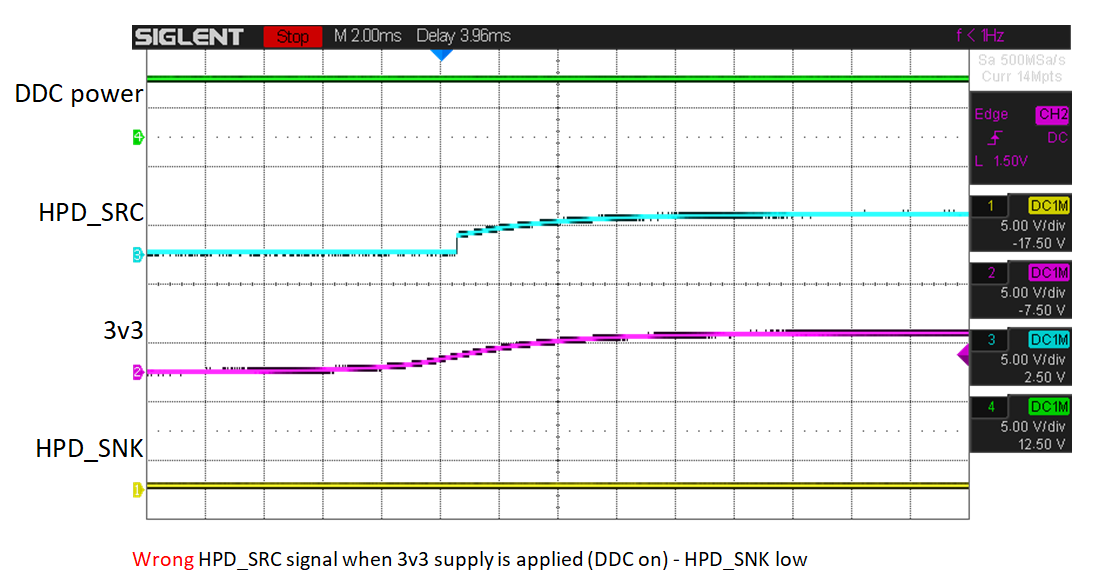

On a specific printed board assembly, one device is faulty responding and gives a HPD_SRC high level while the input HPD_SNK is low.

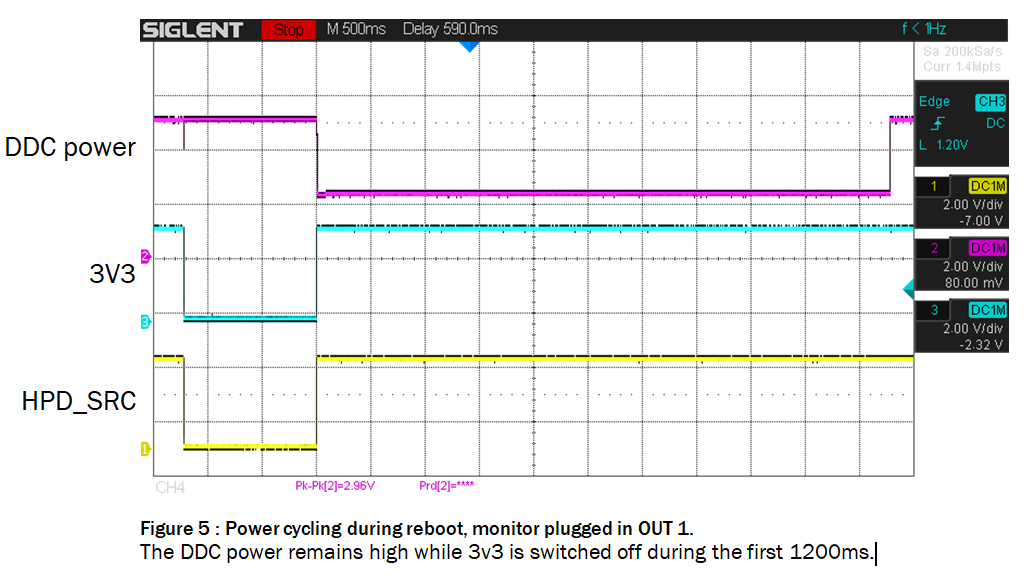

This occurs every time the board is powered cycled but does not always occur when the device is cooled down just before powered on or when the component was not supply for a period longer than tenth of seconds.

The behavior can be reproduced on the printed circuit board without other interfaces connected (base board not plugged in meaning no i2c communications) than the following:

- 3v3 chip supply

- 5V DDC

- No load on HPD_SRC

- External HPD pulled up to 5V DDC or pulled down to ground via 1kOhm

- A forced reset (EN pin tied low during power cycling) did not remove the issue.

- Second Test reading out the FORCE_HPD_SRC bit from the i2C register content does not show unexpected value.