Part Number: TUSB4020BI

Hello,

I have a couple questions about the TUSB4020BI GRSTz input specs. The timing spec is that VDD (+1.1V) and VDD33 (+3.3V) must be stable 3ms before GRSTz is de-asserted.

Question #1: Must this timing spec be met even if the GRSTz pin is subsequently asserted and de-asserted after power up? What happens if the spec is not met at power up? We have processor control of this reset pin, and we could give it a reset pulse if we need to. Or might the hub get into a dangerous state (latch-up, etc.) if the power up reset timing is not met?

This spec says GRSTz must be low for 3ms after the 2 supply voltages are stable. A strict interpretation of this would be:

- For the supply voltages, “stable” means each supply reaches its final level, not just some level close to that level.Or is it 90% of final value?

- GRSTz must be at or below its VIL spec + its min hysteresis spec during the 3ms window. VIL is 0.8V, but there is no min spec on the input hysteresis, so I have to assume it is 0. Therefore, GRSTz must not be above 0.8V for 3ms after both voltages are stable.

Question #2: Is this correct? Or is the spec really that GRSTz must not go above VIH until at least 3ms after both voltages are stable?

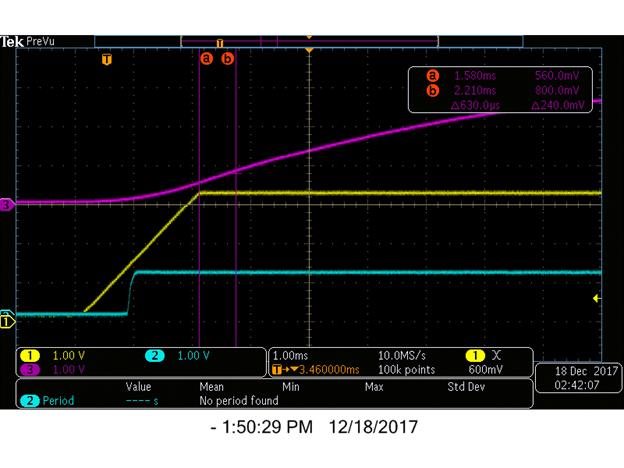

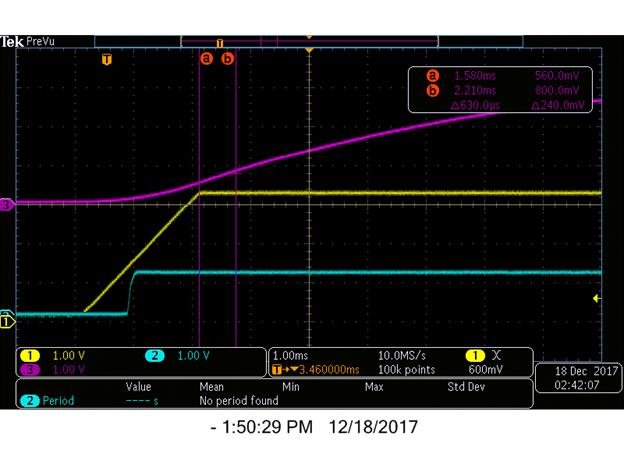

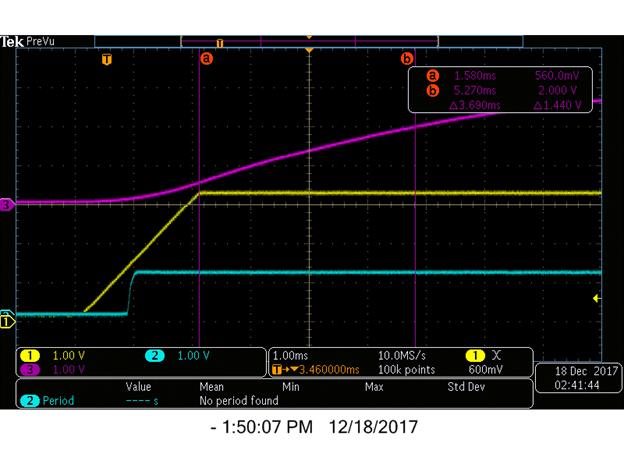

For reference, below is a scope capture (voltages stable to GRSTz=0.8V and GRSTz=2.0V). The hub function is fine in this case, but for the strict interpretation of the spec (0.8V), the reset is low for only 0.44ms after supply voltages stable.

Ch 1: VDD33

Ch 2: VDD

Ch 3: GRSTz

Thanks,

Rohit Joshi