Other Parts Discussed in Thread: DS90UB926Q-Q1

Dear Team,

I have designed a remote camera solution with DS90UB925Q-Q1 and DS90UB926Q-Q1 according to the typical camera application. Figure below is the system block.

I configured DS90UB926Q-Q1 with these configuration instructions, reg_0x07[0x18], reg_0x03[0xF8], reg_0x08[0x20] and reg_0x10[0x20]. All is well.

However, when I configured reg_0x03[0xD2] to reg_0x03[0xD3] of DS90UB925Q-Q1, MCU reported a missing ACK event.

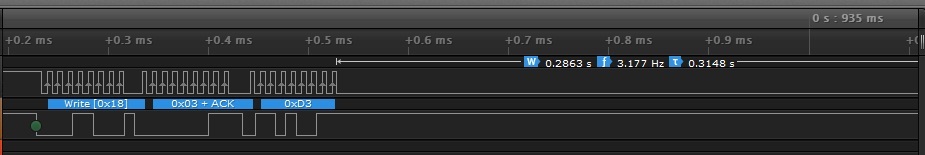

I catched the I2C signals of DS90UB925Q-Q1 which ID was 0x18 with the Logical Analyzer(Of cause I only can catch them from I2C pins between SoC and DS90UB926Q-Q1).

I found that SCL had a long periods of low level. After about 283ms, SCL was free. Then I read back reg_0x03 of DS90UB925Q-Q1, the value was 0xD3.

Why does the write operation of reg_0x03[0xD2] to reg_0x03[0xD3] result in a long periods of low level at SCL and cause the missing ACK event?

Thanks very much.