Other Parts Discussed in Thread: TPS65981EVM, HD3SS460, TPS65981

Hi Team,

Could you tell me how DPSourceSink bit behaves?

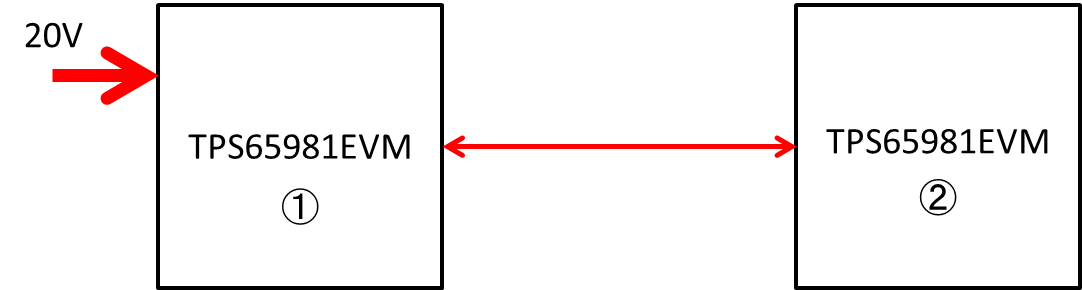

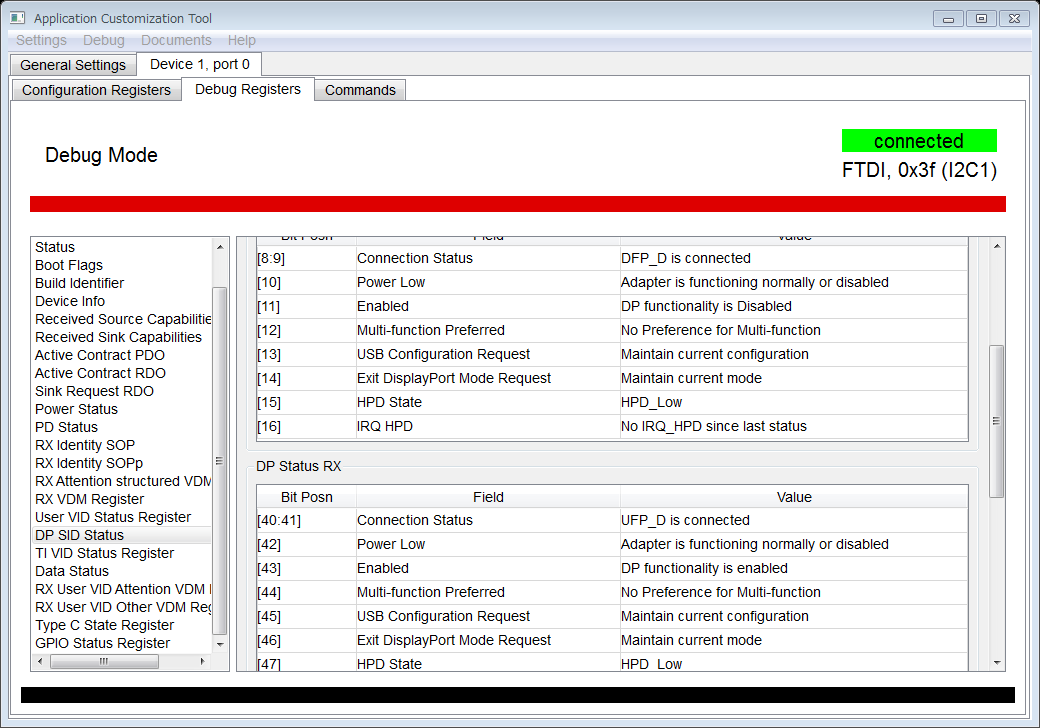

I checked DPSourceSink bit behavior using TPS65981EVM with following condition. But the bit always shows 0b "DP Source (DFP_D) connection requested" on both DFP_D and UFP_D sides. Is this bug?

① TPS65981_HD3SS460_DRP_Source_Advanced_v3_10.tpl

② TPS65981_HD3SS460_DRP_Host_Advanced_v3_10.tpl

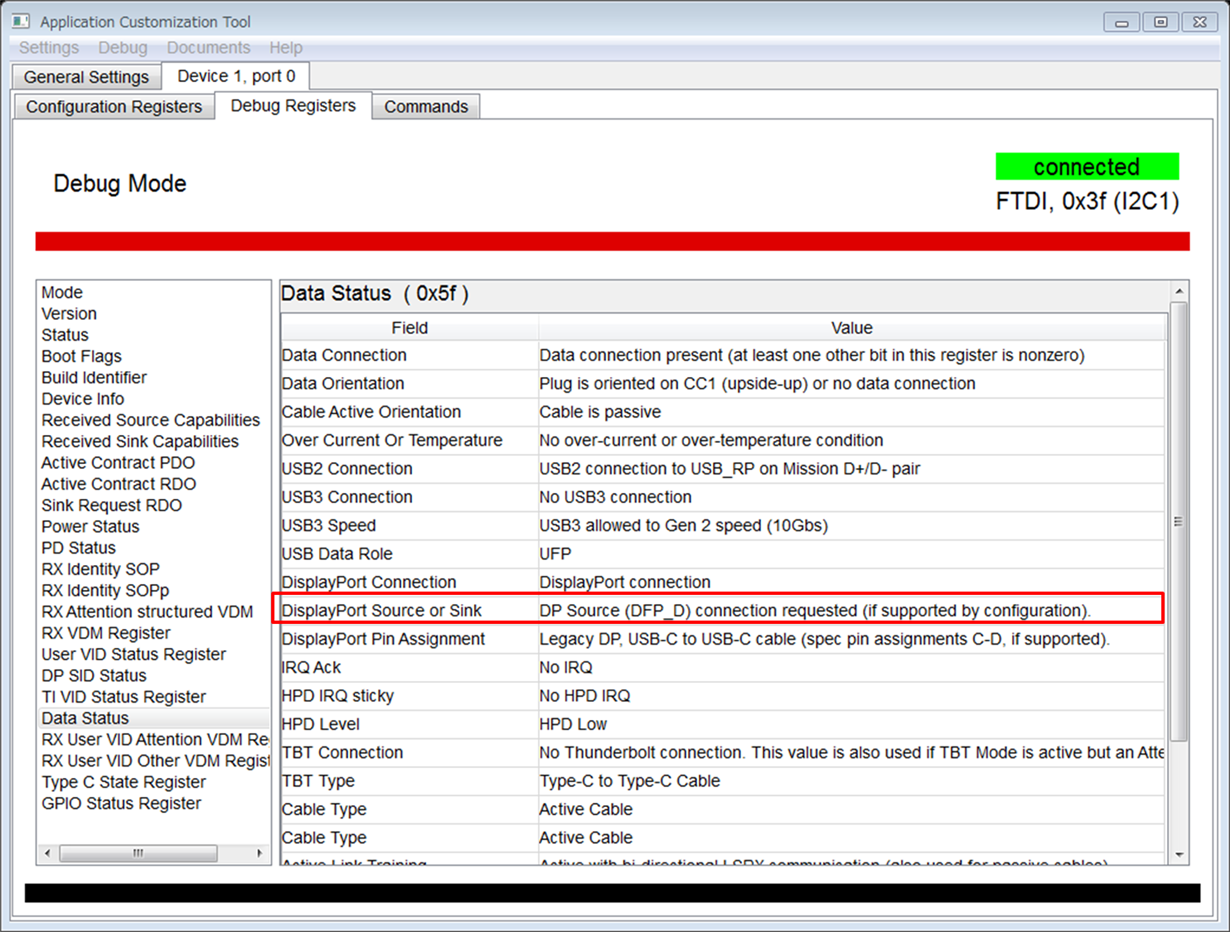

[① Side]

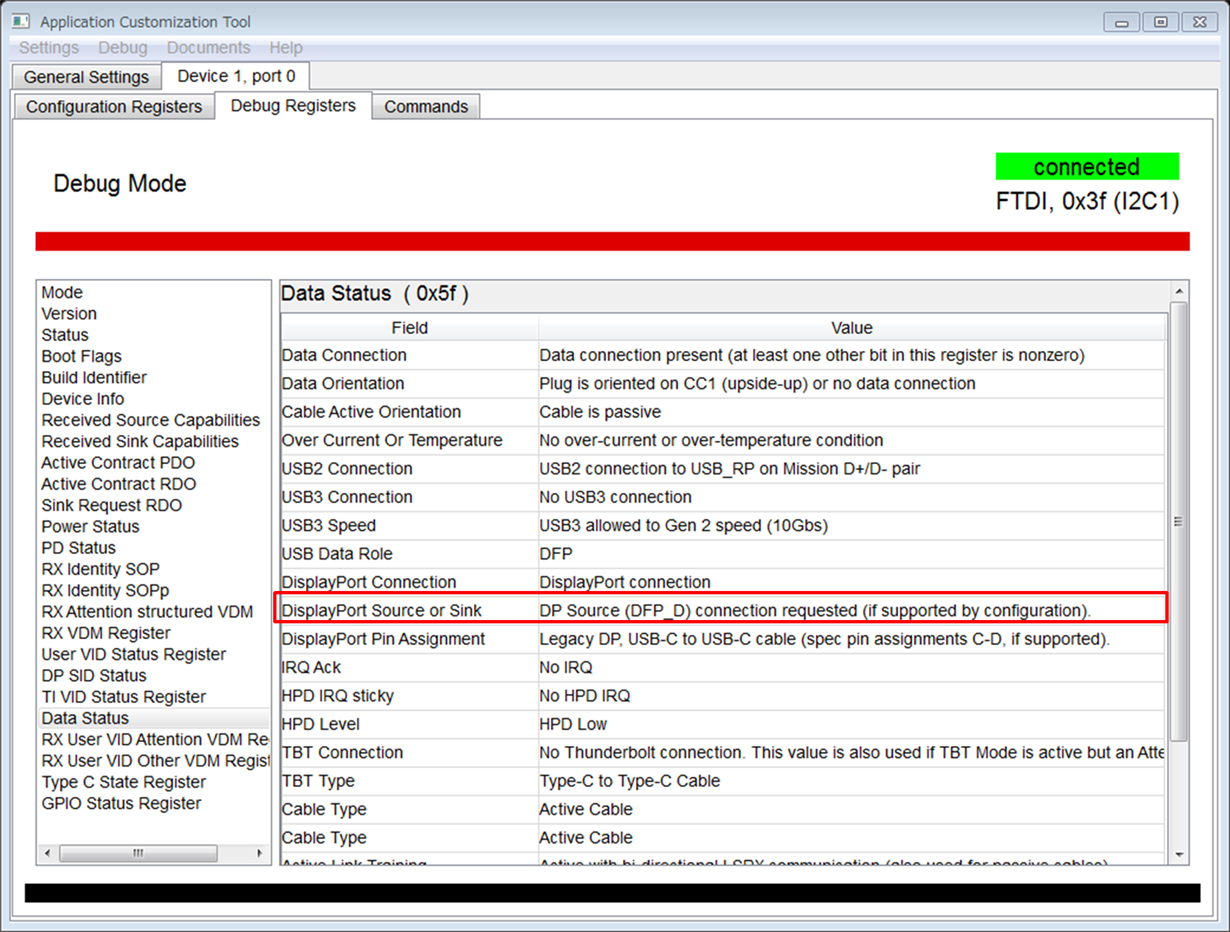

[② side]

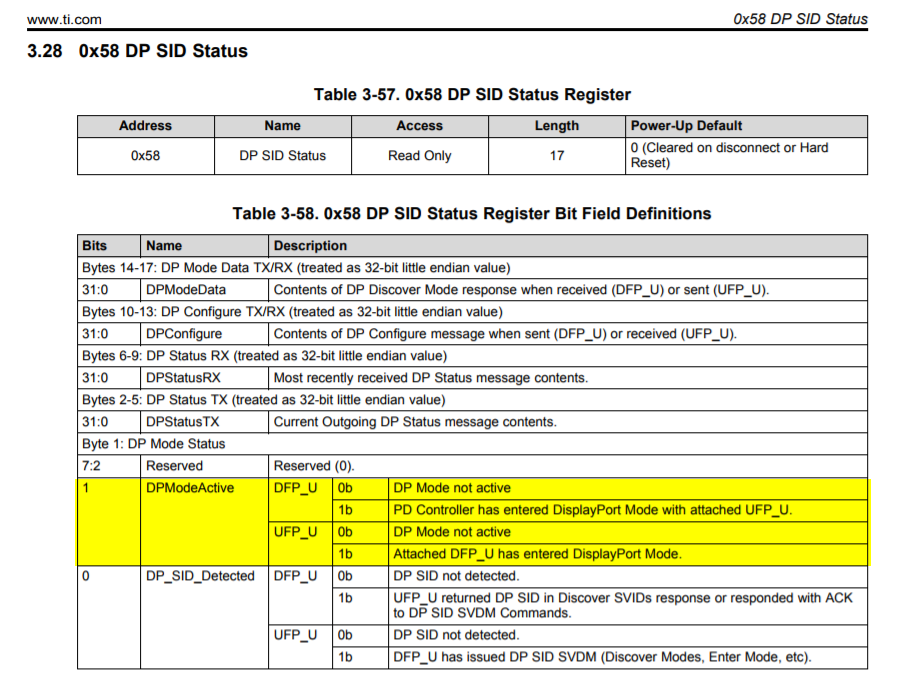

My customer is expecting that EC can judge PD controller is in UFP_D Assignments E condition by the table below. But it is not realizable because DPSourceSink is always 0b.

Regards,

Takashi Onawa