Part Number: UCC21520

Hi, my customer is using UCC21520 to drive a single phase full bridge AC/DC PFC consists of 8 MOSFET(each leg two MOSFET in parallel), each UCC21520 drives one half bridge. Right now they are only switching the low side of the half bridge, the high side is always kept low. The schematics are as below.

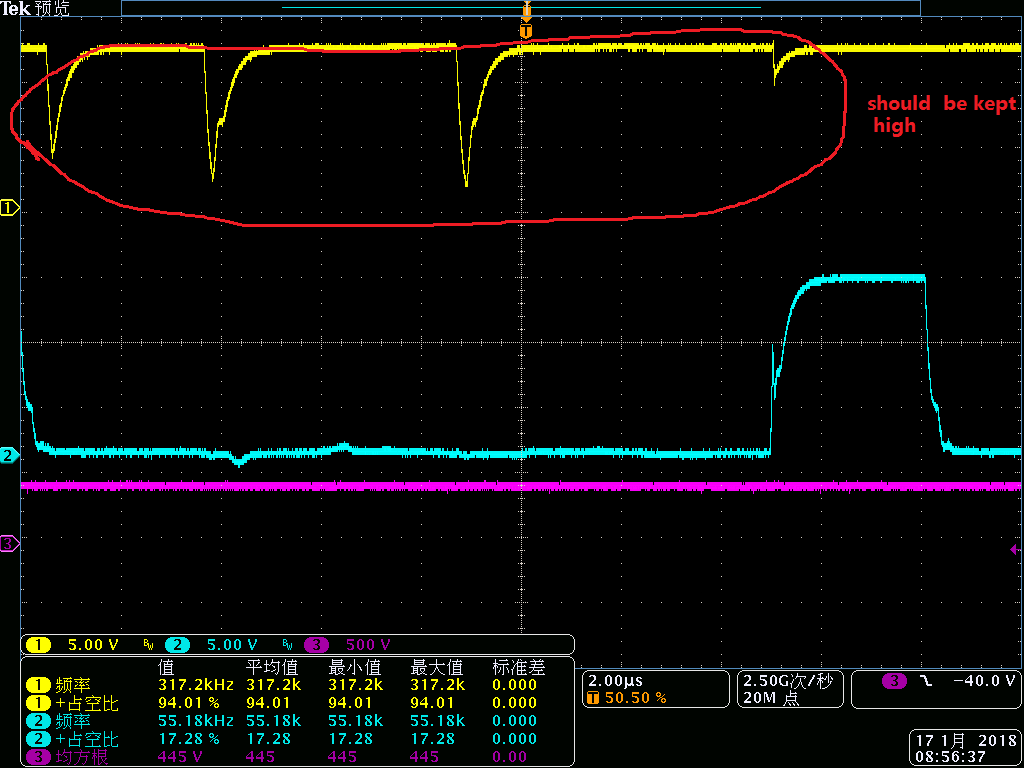

The waveform is as below, the yellow one is the low side MOSFET G-S waveform of phase L half bridge, blue one is the low side MOSFET G-S waveform of phase N half bridge. Since the AC input is 50Hz, 20ms period, each low side should be in high frequency switching mode for 10ms, and be constant high for the other 10ms. We can see that there are a lot of oscillation when the low side MOSFET gate side should be kept high (red circle part in the picture below).

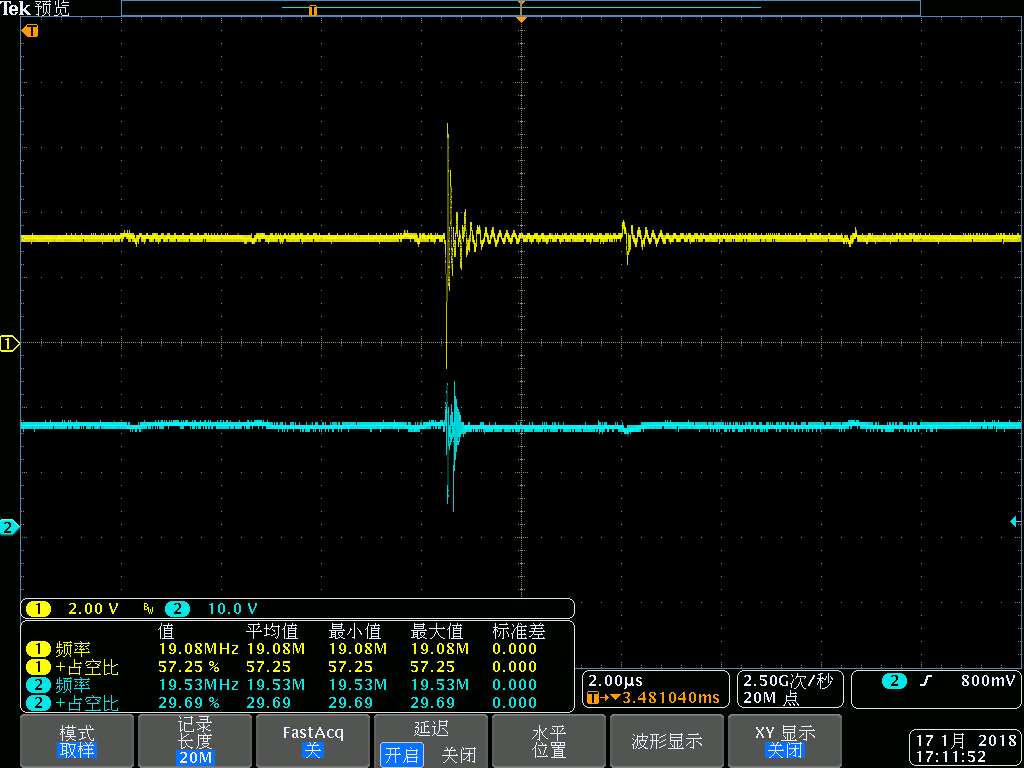

By zooming in, we can see the waveform like:

1. what may cause the spike(or oscillation?) of the G-S waveform and how can we decrease it?

2. For the blue waveform in the picture above, the miller platform is very obvious and the yellow waveform dips at the same time, any way to improve this behavior?