Other Parts Discussed in Thread: TPS65981, CSD16323Q3

Hi, Team

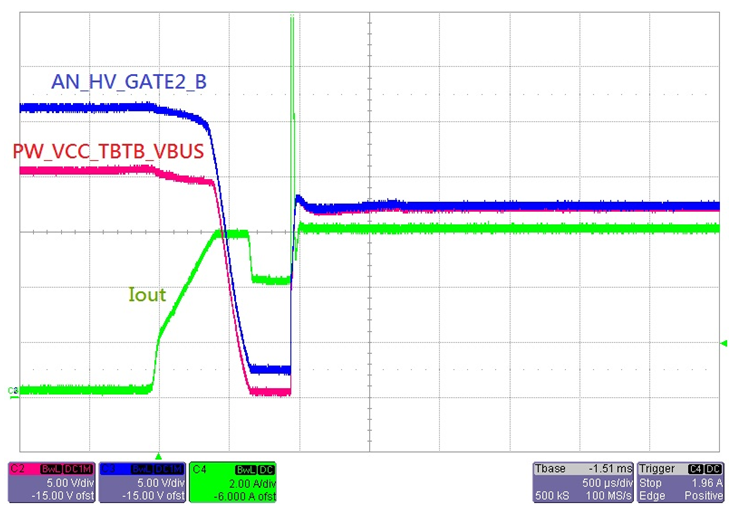

My customer did the OCP test on TPS65983B,

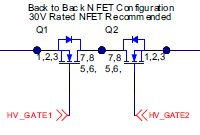

When system tested the OCP at 6A, we found the external FET will be damaged(Q2) .

We found the PD controller will limit output current around 4~5A when over current be detected; then the external MOSFET be damaged(Q2).

Could you please help to check OCP behavior which is normal or abnormal by below waveform?