Part Number: DS80PCI102

Hi,

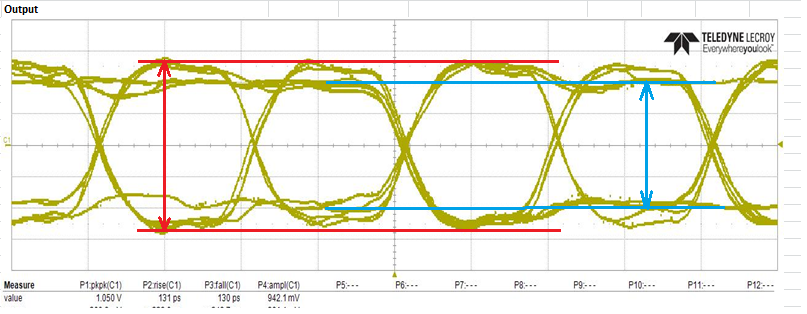

Though my customer is trying to pass PCIe 1.1 Compliance Test, they can not pass below items on their system.

- Tx, Template Tests (PCIE 1.1)

- Tx, Peak Differential Output Voltage (Transition)(PCIE1.1)

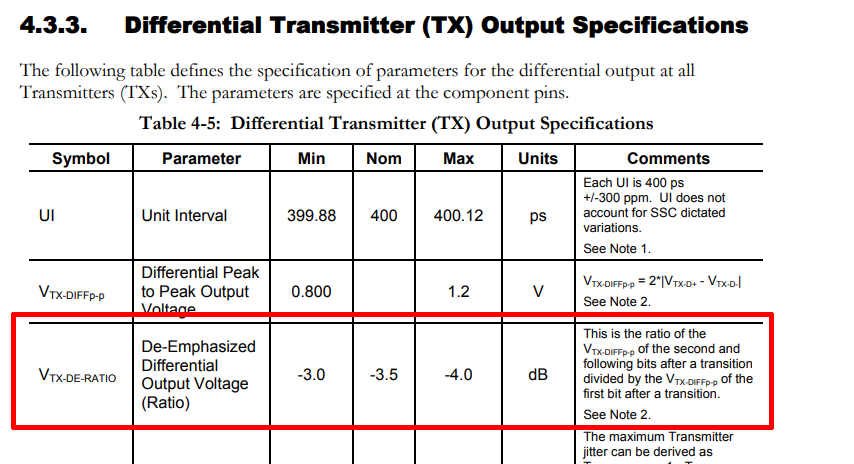

- Tx, Deemphasized Voltage Ratio (PCIE 1.1)

(Another items can be passed.)

Please refer also the attached file.

Setting data seems to be correct as attached.

(EEPROM seems to be read correctly because DONE pin is asserted.)

:10000000000010000004070000ED40000ED4002F97 :10001000AD4002FAD400005F5A8005F5A8005F5A8F :100020008005F5A800005454FFFFFFFFFFFFFFFF0E :10003000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFD0 :10004000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFC0 :10005000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFB0 :10006000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFA0 :10007000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF90 :10008000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF80 :10009000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF70 :1000A000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF60 :1000B000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF50 :1000C000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF40 :1000D000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF30 :1000E000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF20 :1000F000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF10 :10010000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF :10011000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFEF :10012000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFDF :10013000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFCF :10014000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFBF :10015000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFAF :10016000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF9F :10017000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF8F :10018000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF7F :10019000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF6F :1001A000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF5F :1001B000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF4F :1001C000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF3F :1001D000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF2F :1001E000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF1F :1001F000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF0F :00000001FF

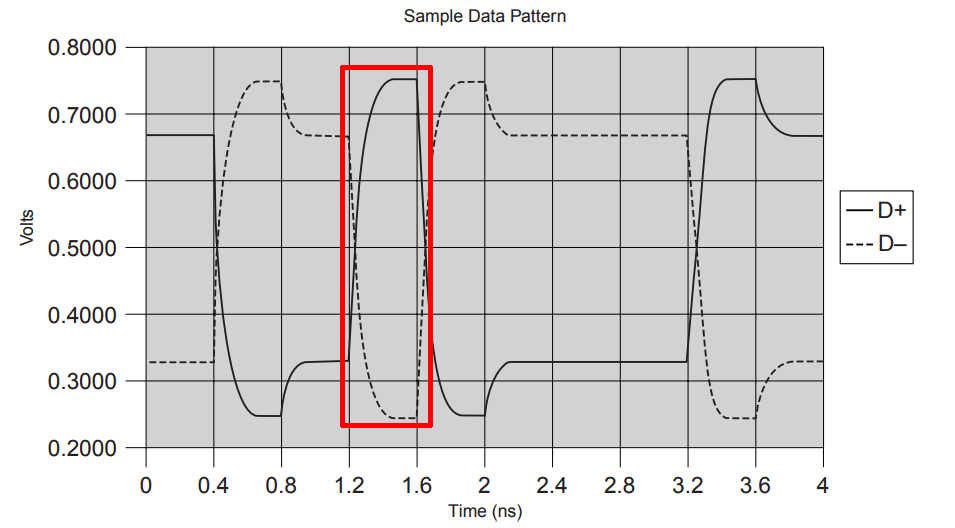

Though DEM is set to -3.5B, the effect of deemphasis only 0.6dB according to above test results of "Deemphasized Voltage Ratio (PCIE 1.1)".

What is the cause to reduce effect of deemphasis?

Should we set deephasis more stronger(i.e. -6dB, -9dB)?

Please send me email(kuramochi@fujiele.co.jp) if you need more information(i.e. a detail of test results, schematic).

Best Regards,

Kuramochi