Dear Guys,

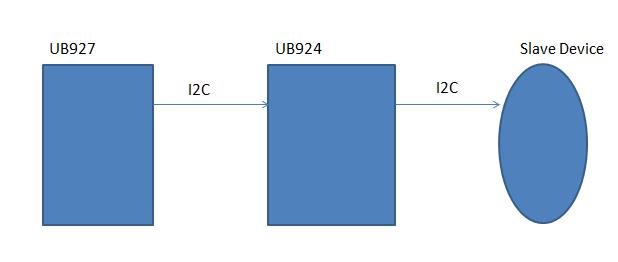

Here is structure as customer application as below, READ/WRITE will abnormal no matter UB927 communicate to UB924 or UB924 communicate to Slave device.

We think it should cause by i2c clock stretching and would like to check if it can be adjust by some way such as register setting….

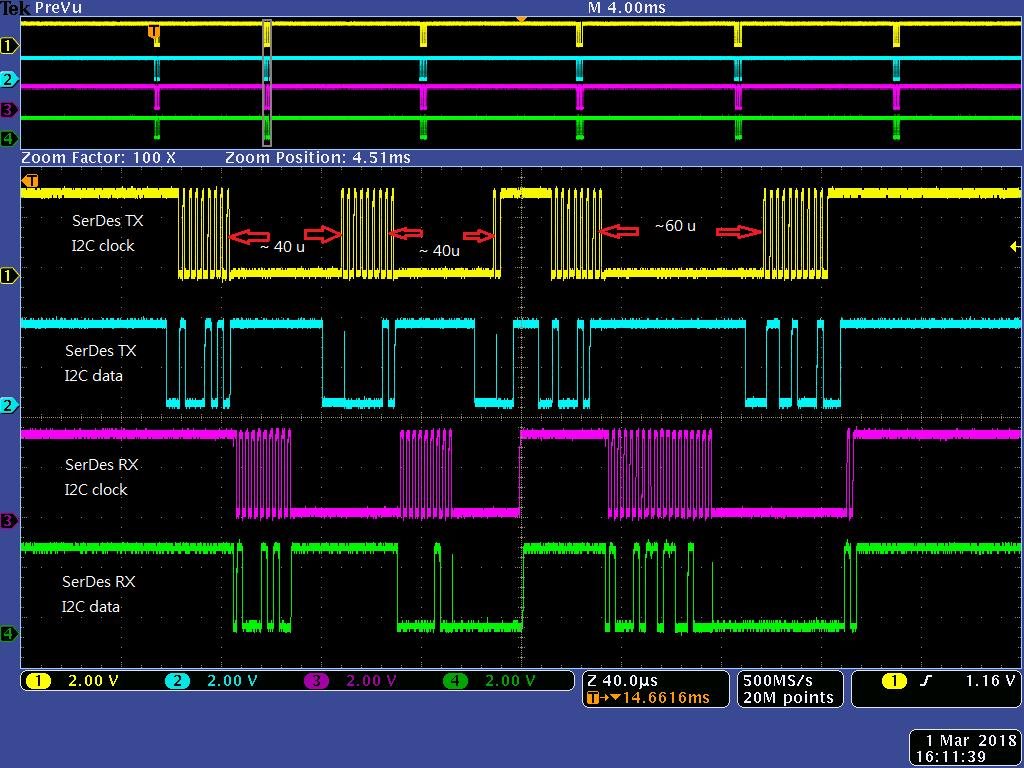

Please refer to the below waveform.

It’s a i2c read operation to the remote slave device after UB924 where the i2c host is at the front of UB927.

As you can see, 40 usec and 60usec are the clock stretching period caused by SerDes TX. Could those stretching time be adjustable of the SerDes configuration?

Thanks,Ian.