Part Number: HD3SS3220

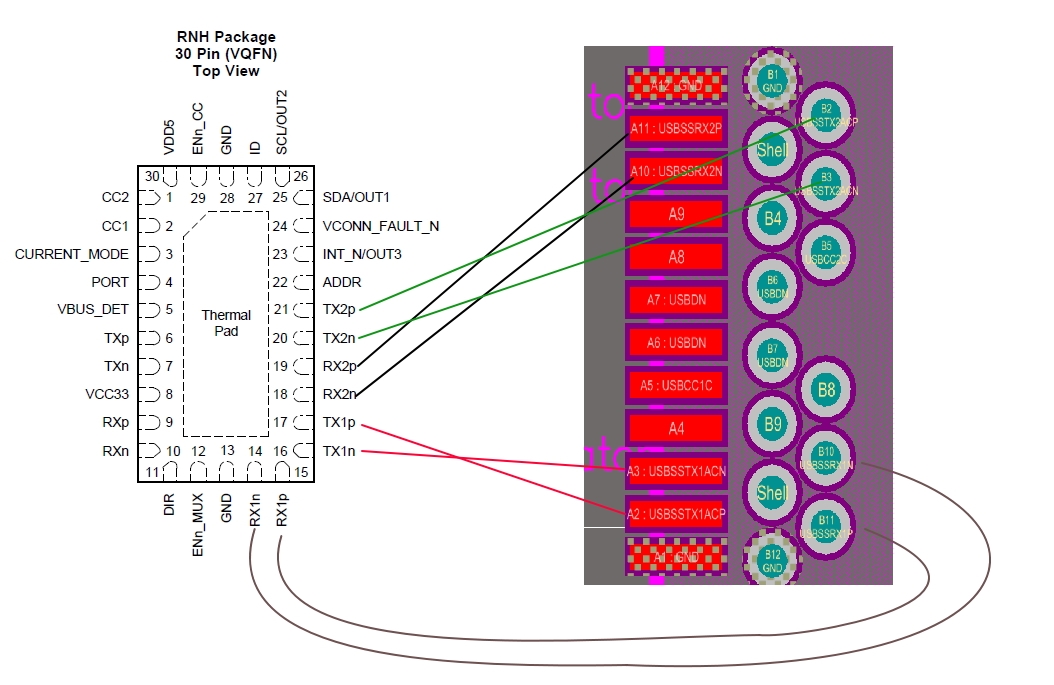

When I placed the HD3SS3220 and my Type C connector (WURTH 632723300011) on the same side of my PCB, most of the signal connections and the routing options seemed reasonable. However there appears to be a cross Tx1P & TX1n shown in red in the diagram below ? (I double checked the pinout of the connector and it is correct)