I have 2 questions I hope you can help answer:

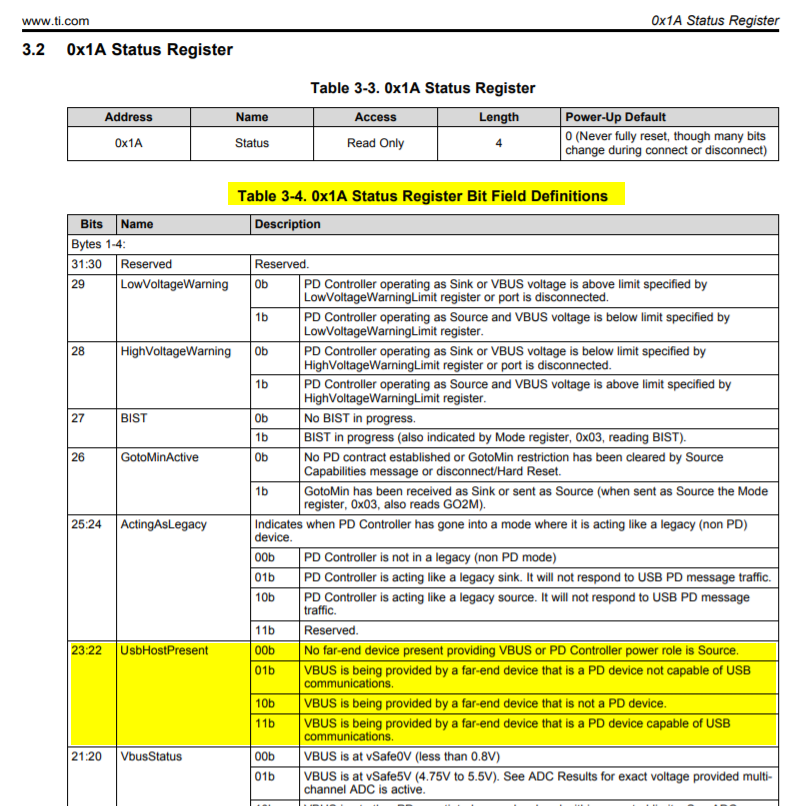

- Is there any known reasons that the UsbHostPresent bits may not get set to something other than [00], when configured as an UFP and VBUS is definitely present? Using these bits by the O/S to know when charger is present, but not getting reliable results.

- We have potential for bus contention on SPI between TPS65986 and other device talking to SPI Flash. After initialization, TPS65986 is not supposed to access Flash anymore, but we're finding that some conditions (believed to be PD Protocol Errors) are causing POR event, and of course it then needs to access Flash to re-initialize.

- Is this expected for possible Protocol Errors to cause POR? (or other events not related to disruption of power to the device)

- To avoid contention, currently using the TPS65986 Chip-select to disable SPI buffer between other Host and SPI Flash. This works to isolate that Host from the bus, but worried it could cause a first read attempt failure when TPS65986 tries to boot. If first read fails, will it try again, or go to alternate boot-mode (which we don't support)?