Part Number: SN65DSI83

Hello.

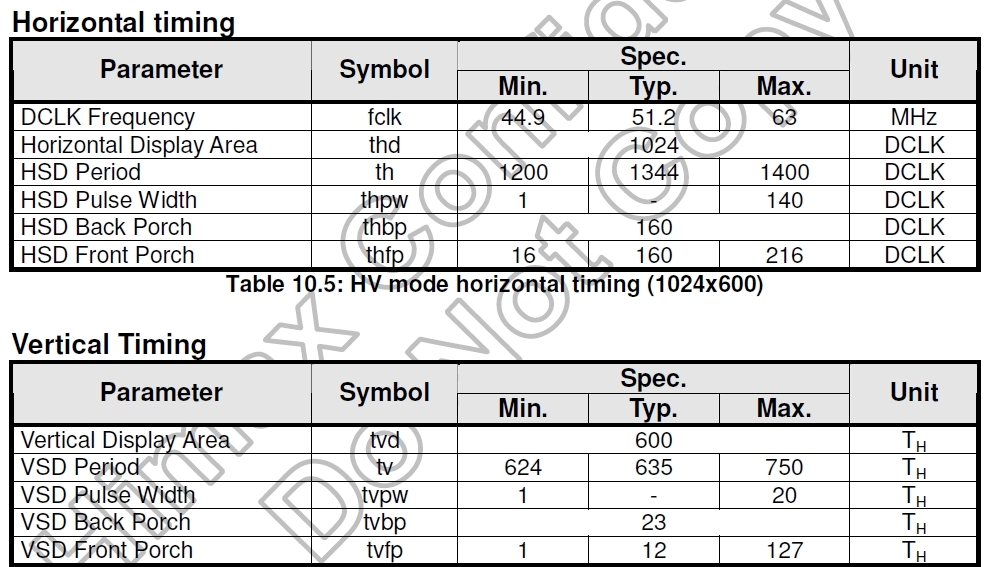

I'm developing an application for an STM32F769 which has a 2-lane DSI host and will be connected to a 1024x600 18bpp LVDS panel.

I managed to get the panel working and display the test pattern on it, but I'm unable to get any image from the MCU.

For developing this application I started with a DSI to HDMI adapter, the code was adapted for 1024x600 resolution, and it displays correctly at 42.3Hz with a DSI speed of 400Mbit/s per lane, non-burst mode with sync pulses. That way I know that DSI stream is working.

Tested the panel at various clock rates and it should be able to work at this refresh rate using a clock frequency of about 25MHz

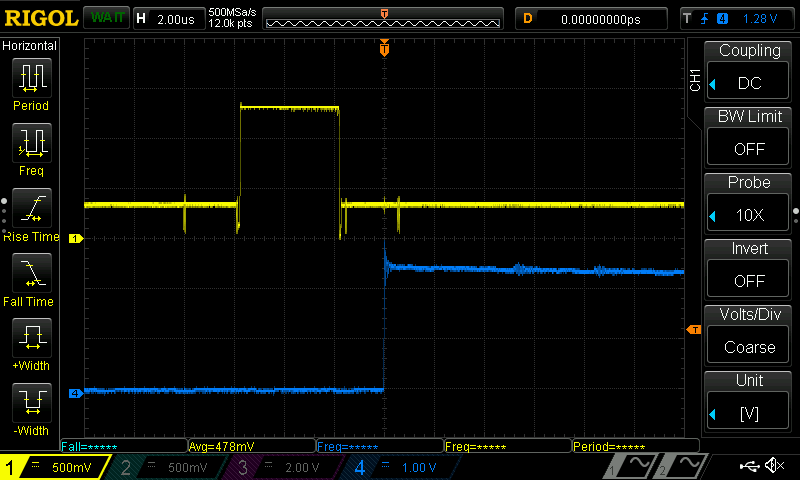

When debugging the SN65DSI83 what I find is that the LVDS stream is never started, and it generates a sync error interrupt (bit 7 of register 0xE5 is set all the time even if I clear it)

LVDS clock is generated from DSI clock, I made sure that DSI clock is continuous, there are no PLL errors.

The start sequence was also checked so when EN is asserted all lanes are in LP11, after 20ms registers are setup, then video stream is started and after that the PLL is enabled and a soft reset is sent to the SN65DSI83

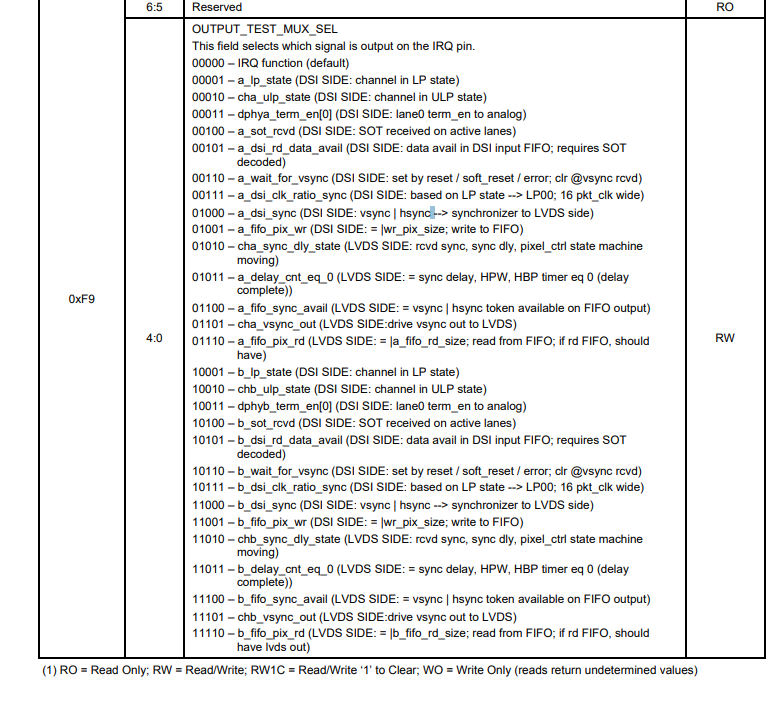

What can be the cause of this sync error? It appears as soon as the stream is started, the IRQ line was configured and it goes high right after starting the stream. When starting the PLL it is also cleared and goes high again at the beginning of next frame.

I checked the settings with DSI Tuner and it should be ok, the minimum clock is 150MHz and the system is setup for 200MHz (400mbps)

Thanks for your help.