Part Number: DS250DF210

Other Parts Discussed in Thread: DS125DF1610, , DS250DF410

Hello,

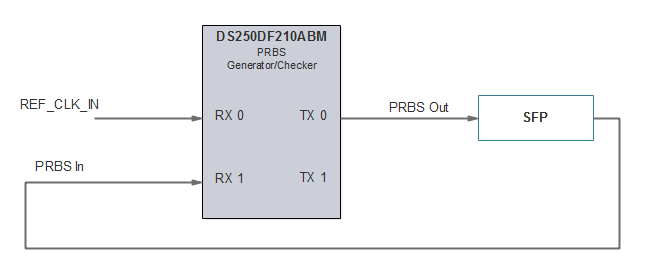

Our customer would like to add a cable tester to their design. Using the DS125DF1610 BERT Tester Reference Design as an example, we would utilize the PRBS Generator of one channel of a DS250DF210 and the other channel use as the PRBS Checker . Below is a diagram the basic concept.

We assumed that the PRBS GEN/CHECK core is similar if not the same as used in the DS125DF1610.

In our experience with the DS125DF1610 the following is true:

a. You cannot operate the Generator and Checker on the same channel simultaneously

b. You must have an input signal that is a factor of a multiple of 2 of the desired line rate on the Generator's input in order for the Generator to create a pattern that can be checked by a PRBS Checker.

We have the following questions:

1. What are the limits of the multiples of 2 of the desired line rate that must be present on the input in order for the PRBS Generator to operate at Line Rate?

2. Our customer's maximum data rate is 10G Ethernet. Is there a common Reference Clock Rate that could allow us to test both 10GbE and 1GbE without changing the REF_CLK_IN Frequency?

3. The Crosspoint Switch aside, Is there an advantage of using the DS250DF410 over the DS250DF210 in this particular application?