Part Number: SN65DSI83

Dear ,

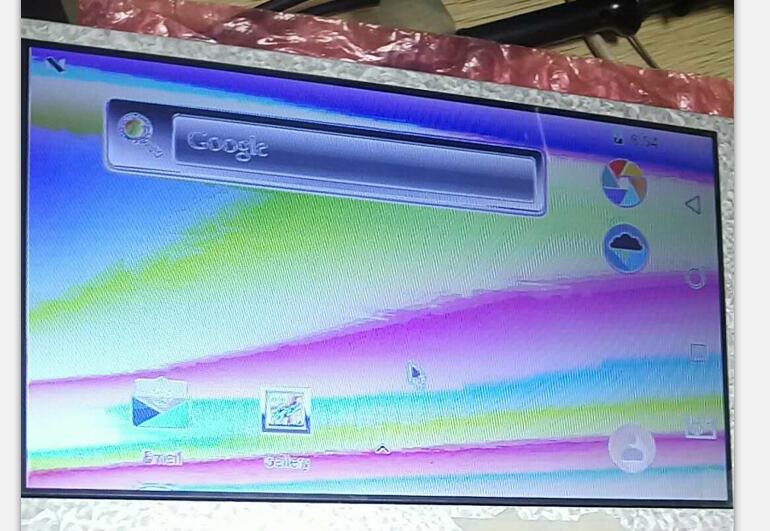

This project si RK3399 -> SN65DSI83 -> 1024X600lvds screen;

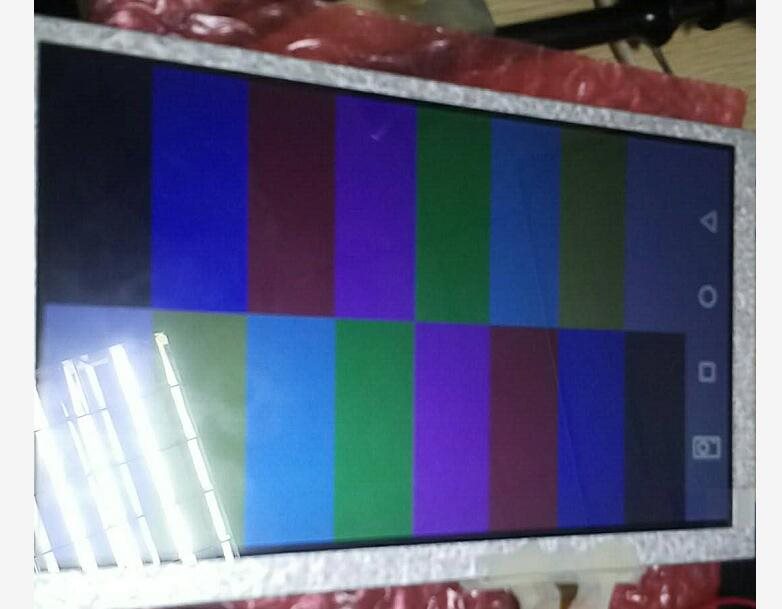

Now the CPU(RK3399) Can't display through sn65dsi83,but test pattern is ok,

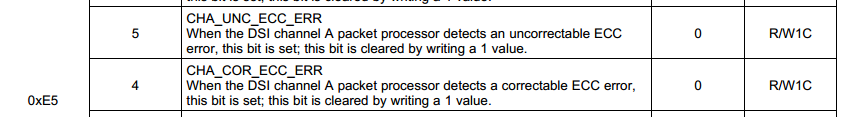

1.read 0XE5 = 80,--what situation wil have this err report ;

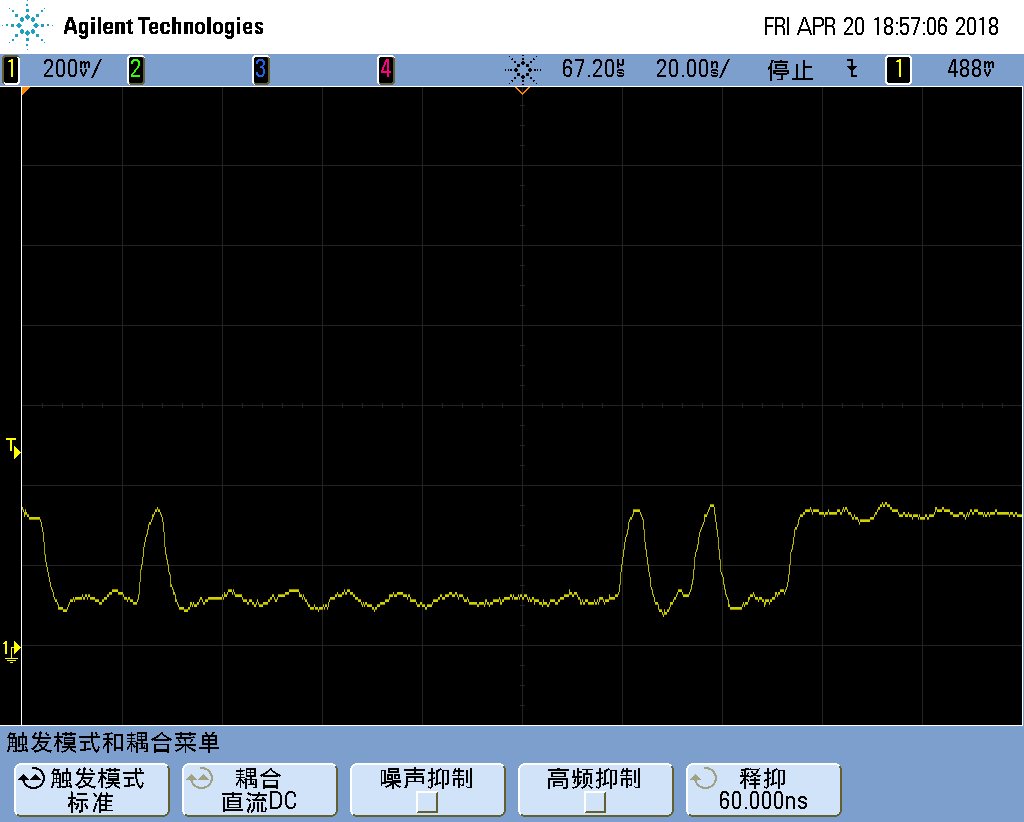

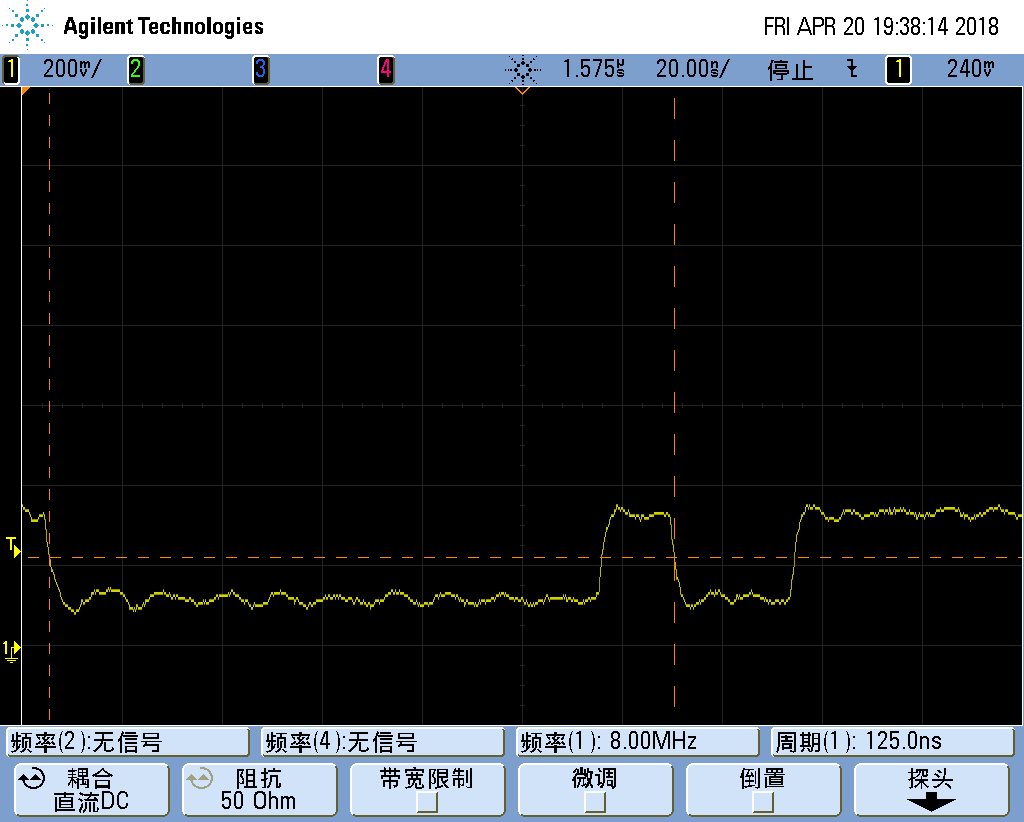

2.Oscillograph probe test on data lane,there willbe two error below:

3.Before EN pull high there is more than 10ms low;

4.HSS, 0x21 0x00 0x00 0x12

5.VSS_ one package incloue four bytes,0x01 0x00 0x00 0x07

6.

before change SOT,SYNC ERROR report,after change SOT error report.

For normal SOT is ok ,DSI83 can recognise this sequence,but maybe receiving VSS and HSS package the err report .I haved checked the wave , it is right;

7.log:

rk3399_all:/ # echo 0xe5 0xff > /dev/misc_test

[ 317.960578] bridge-sn65dsi85 1-002d: [drm:write_dsi85] write reg 0xE5 <- 0xFF (res=0)

rk3399_all:/ # echo 0xe5 > /dev/misc_test

[ 319.025060] e5:80

Please help us to check and solove this issue.

TKS!

Ifpossible you can join my weichat,,id:zero-wo.