We are planning to use DS90UB948 deserilizer with attached JDI display ,

And seriliser as DS90UB929 ,

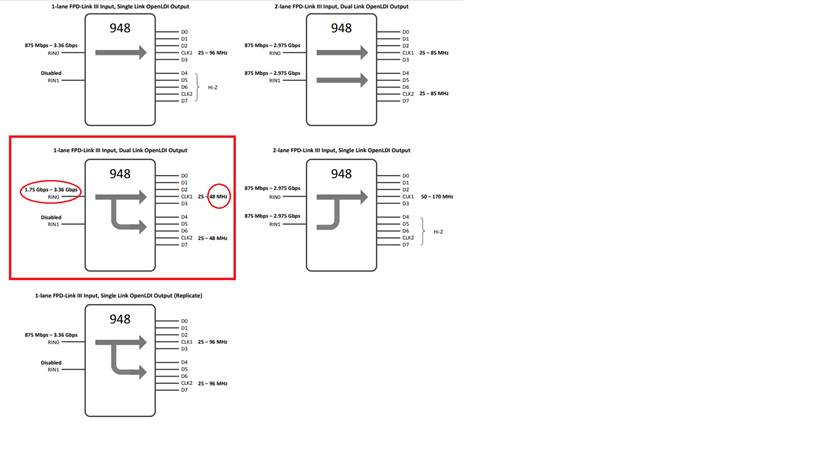

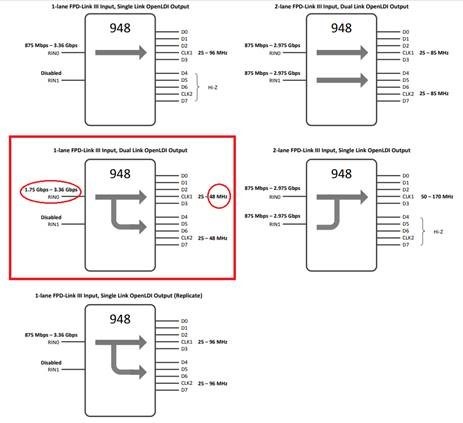

Deserilizer LVDS configuration as given below ,

1- Display frequency is 55Mhz , but desrilizer Max frequency is 48Mhz ,will it be any issue?

2- Seriliser DS90UB929 is fixed and display is also Fixed , is there any solution to use any other desrilizer ?