Part Number: HD3SS3415

Other Parts Discussed in Thread: DS80PCI810

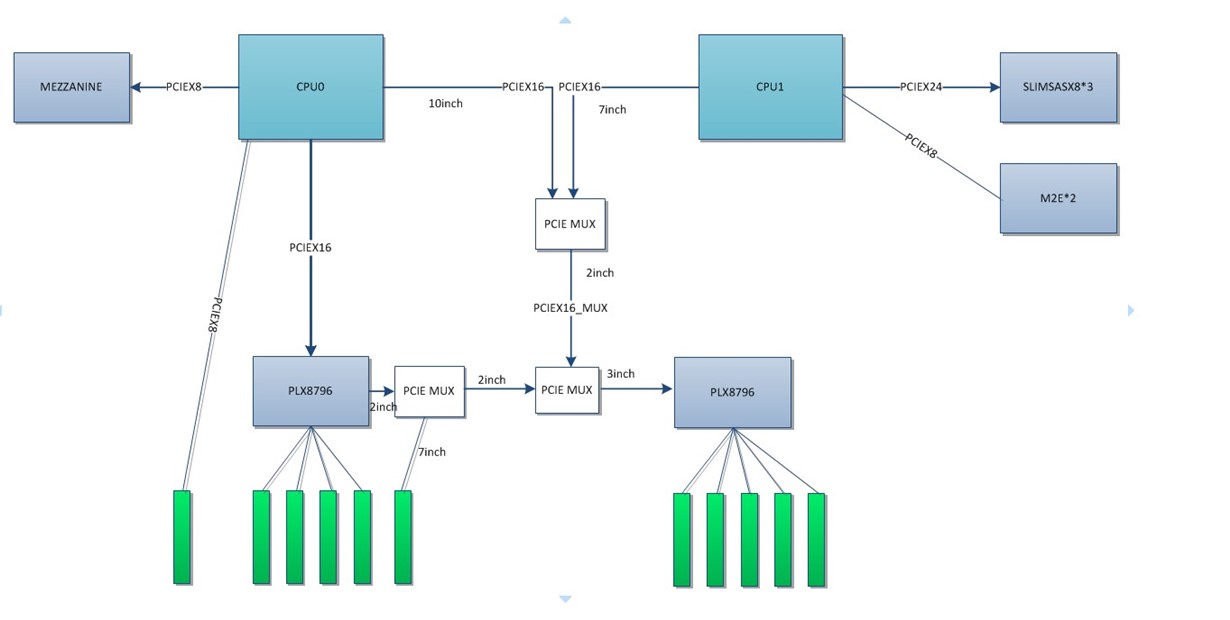

The GPU Server Which Support Intel Purley 2S Platform , and Combine 2 PLX8796 PCIE Switches. Implementing CPU0/CPU1 PCIE root switching through TI HD3SS3415 , Which Tuopu as blow:

1.With a two-stage PCIE MUX:HD3SS3415, is this solution feasible and can you implement PCIE free switching?

2.The length of the PCB trace has been marked as follows. After the CPU0 or CPU1 passes the two stages of the PCIe MUX:HD3SS3415, the PCIE SWITCH PLX8796 is reached. Can the signal rate reach 12Gb/s?

3.Need to add PCIE RE-DRIVER?

4.Is there a delay in PCIE signal transmission?