Other Parts Discussed in Thread: DS90UB914A-Q1

i want to understand the communication over the FPD-Link III.

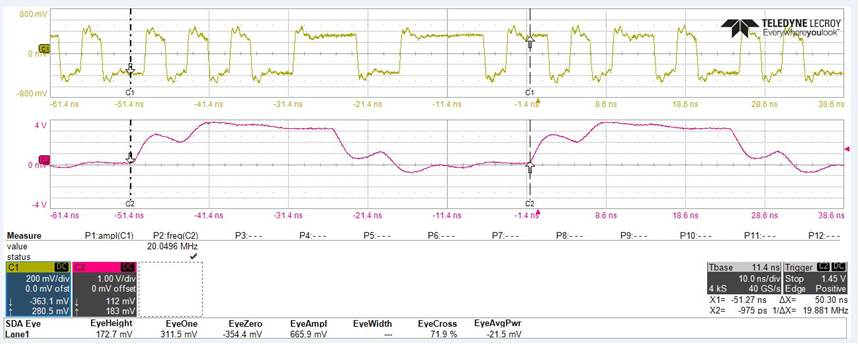

For the following measurement these settings were adjusted.

Serializer: DS90UB913A

Deserializer: DS90UB914A

PCLK: 20MHz

The Chanel 1 shows die CML monitor and the Channel 2 the PCLK. (Measured with Teledyne SDA 820Zi-B)

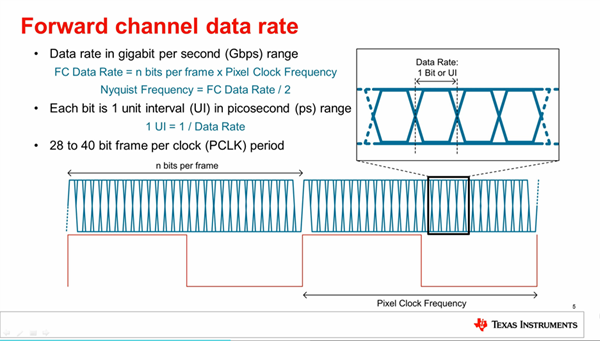

The datasheet ds90ub914a-q1.pdf an the TI FPD-Link University gives the following information:

8.3.1 Serial Frame Format

The High Speed Forward Channel is composed of 28 bits of data containing video data, sync signals, I2C and

parity bits. This data payload is optimized for signal transmission over an AC-coupled link. Data is randomized,

balanced and scrambled. The 28-bit frame structure changes in the 12-bit low frequency mode, 12-bit high

frequency mode and the 10-bit mode internally and is seamless to the customer. The bidirectional control

channel data is transferred over the single serial link along with the high-speed forward data. This architecture

provides a full duplex low speed forward and backward path across the serial link together with a high speed

forward channel without the dependence on the video blanking phase.

On the scope I only count 18 bits per frame, not 28 as expected. Where is my mistake?

Could you please show me the decoding of a frame. How many bits are using for videoinformation, how many

for I2C, how many for for sync and how many bits are use for parity check?

Do you use 8b/10b coding for sending the information balanced?