Part Number: DS64BR111

We have developed a COM Express Carrier board with a SATA III interface to connect to SSD. The carrier board hosts a COM Express module with Intel CPU. On the carrier board itself is DS64BR111. The overall link is: Intel CPU -> COM Express Connector -> DS64BR111 -> 7 Pin SATA Connector -> Cable -> SSD.

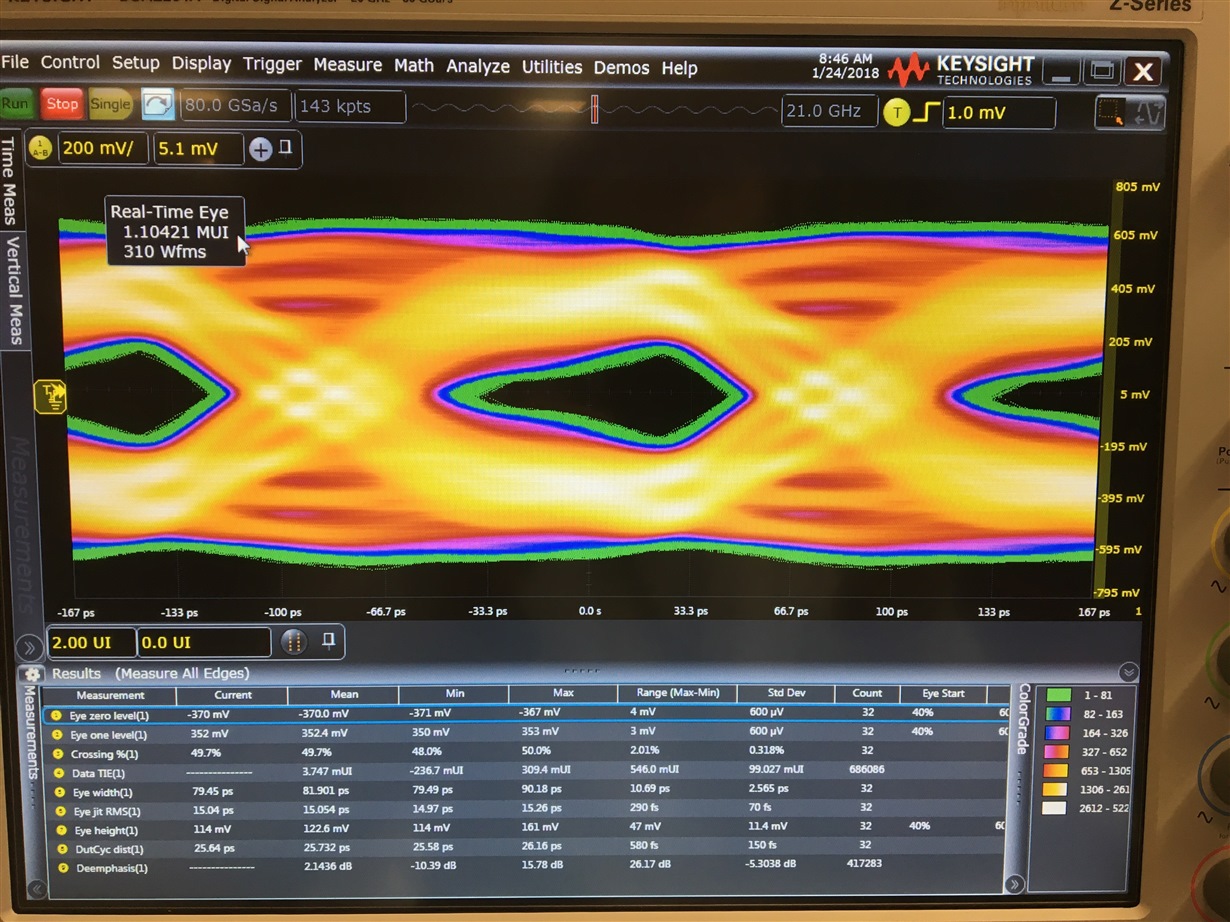

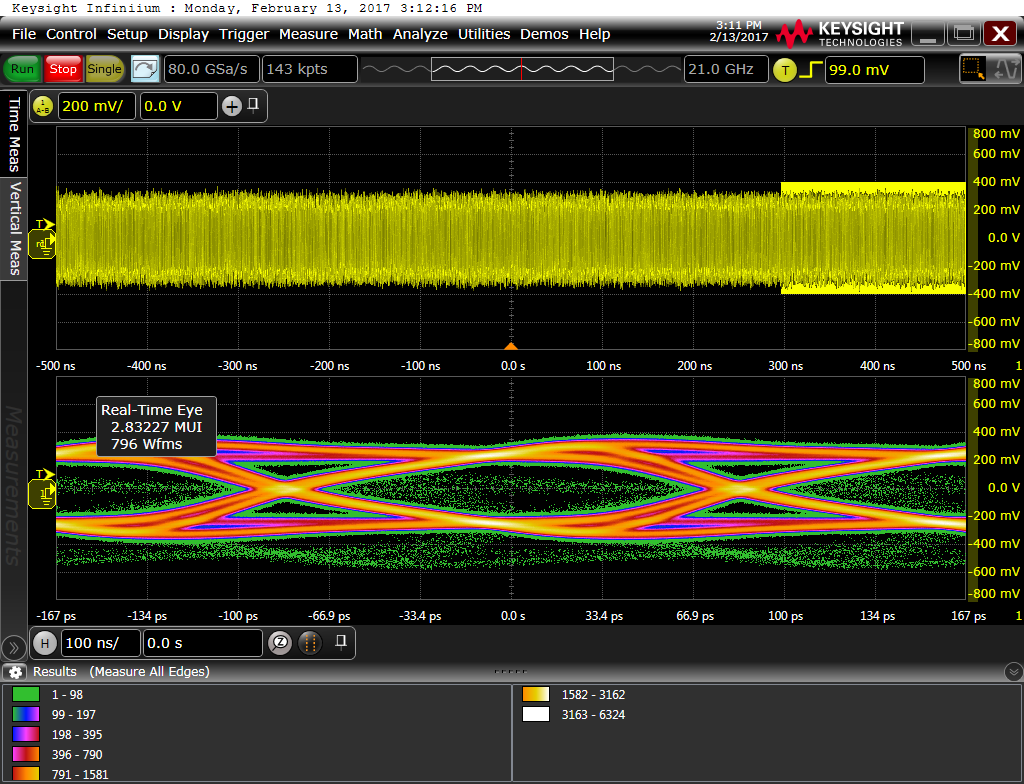

We have experienced intermittent problems with reliability of SATA link between Intel CPU and SSD. We are in the process of determining root cause. One area of concern is signal integrity of SATA link; we have seen errors reported in OS and SMART statistics of drive that indicate there are occasional CRC errors detected by the drive. Sometimes the drive is not detected by the OS at boot time, and other times it is detected and later has errors which causes the filesystem to be remounted read-only. I have tried to tune the link via DS64BR111 settings, but I haven’t been able to measurably improve the situation.

Any help here? We may want to pull this over email as well.

Thanks,

David