Hi team,

My customer is using SN65DSI84 to convert DSI to LVDS. We followed the setup sequence below but can’t get lock. Could you help check what’s the matter? We also want to know in what condition can we get lock? As long as our DSI clock is good? Or the DSI data may also affect lock?

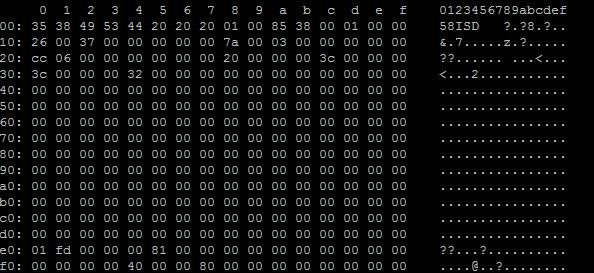

The system is Intel X86 --> DSI84 --> panel. The clk of CSI is about 277MHz, so we set 0X12 to 0x37.

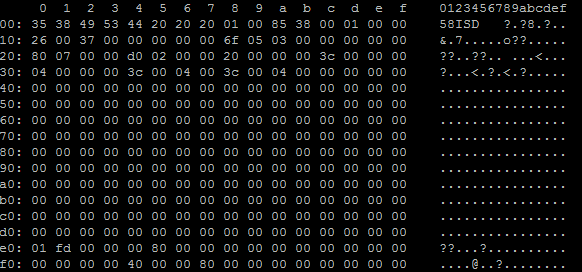

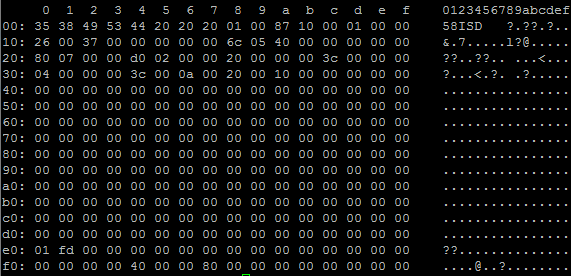

1、The register dump is as below, you can see E5 is 81:

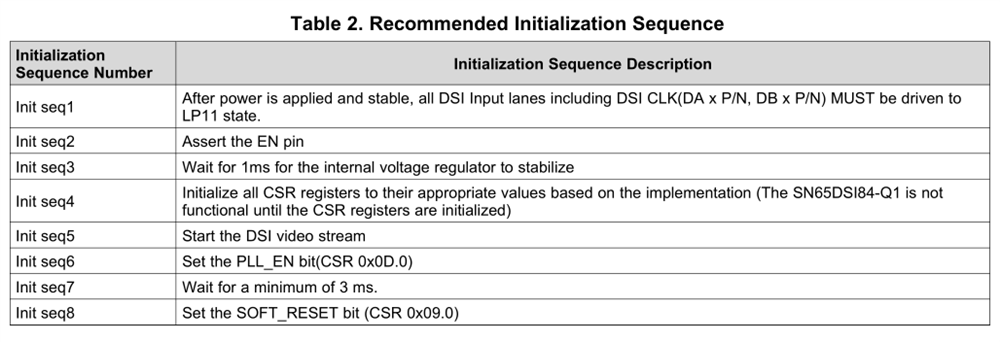

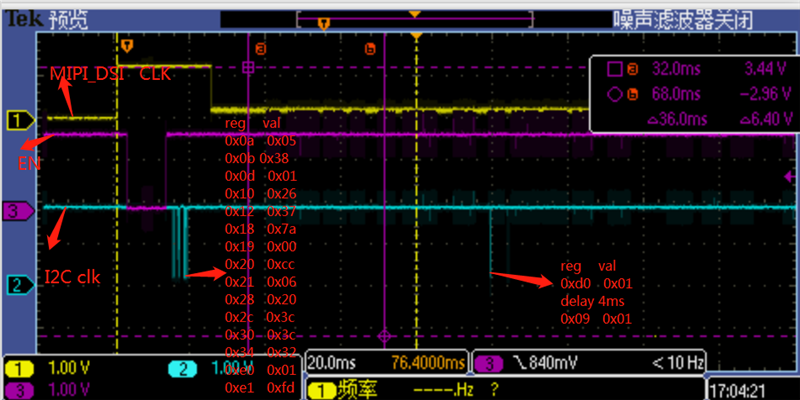

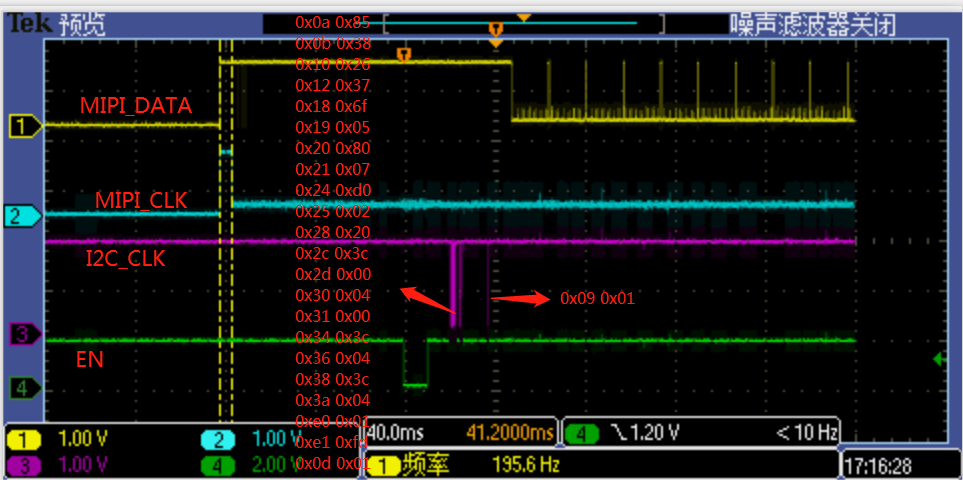

2、Our initialization Sequence:

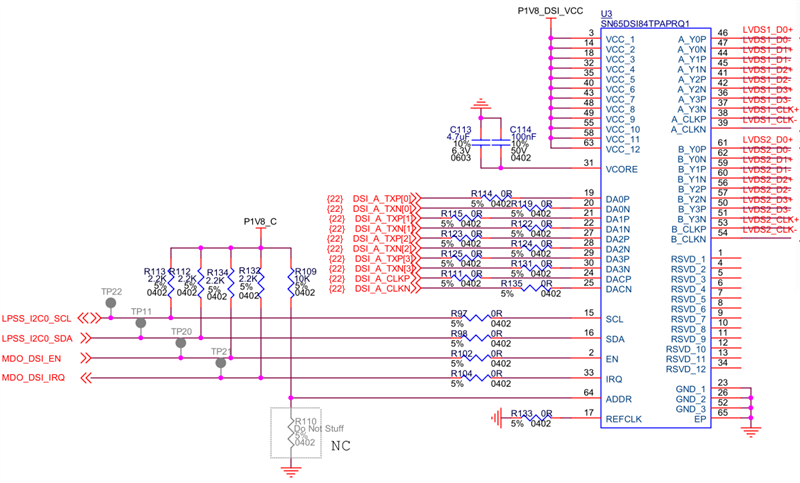

3、Our schematic:

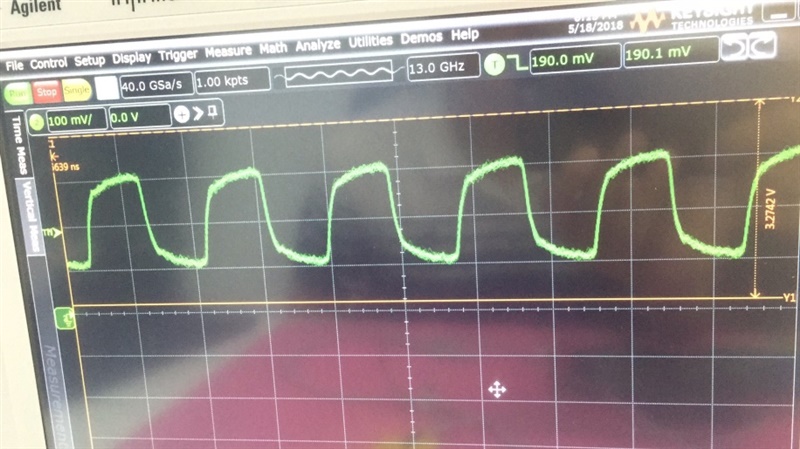

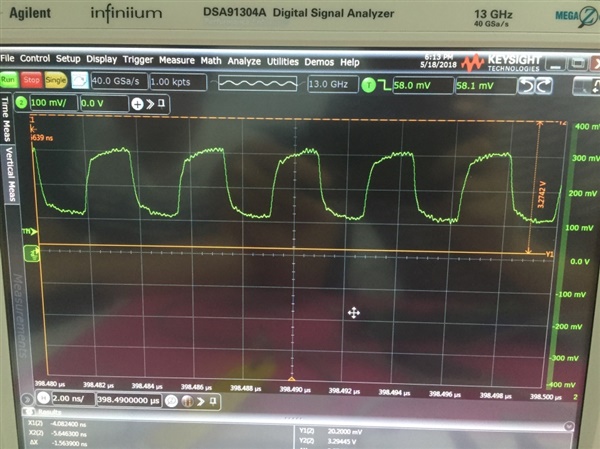

4. Our clock waveform is as below:

Is there anything wrong with our setup?

Thanks,

cera