Part Number: TCA9555

Hi,

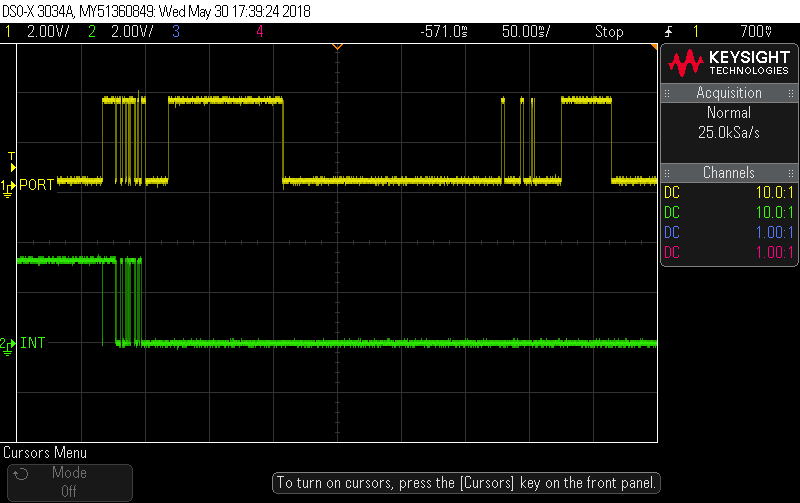

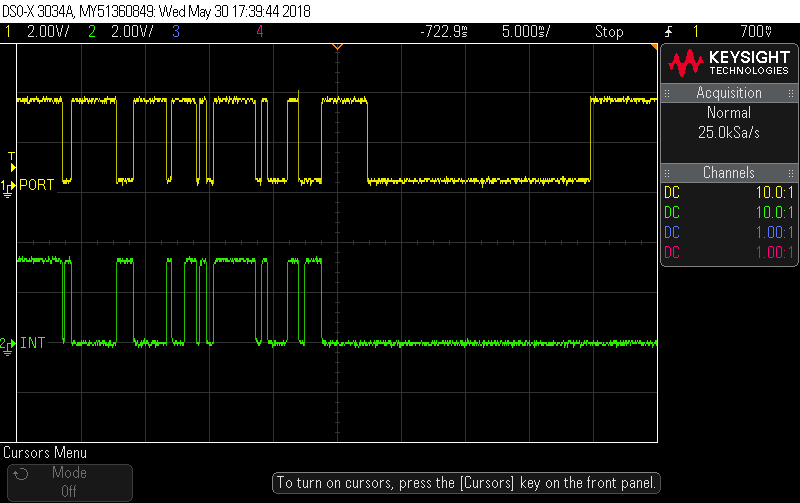

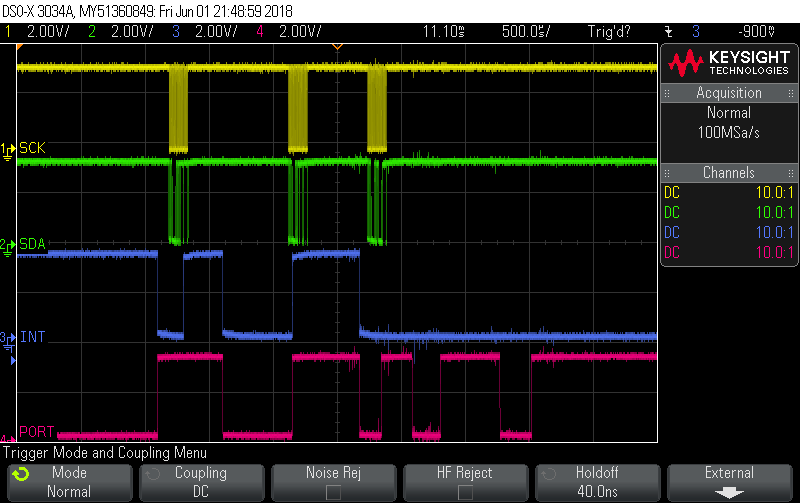

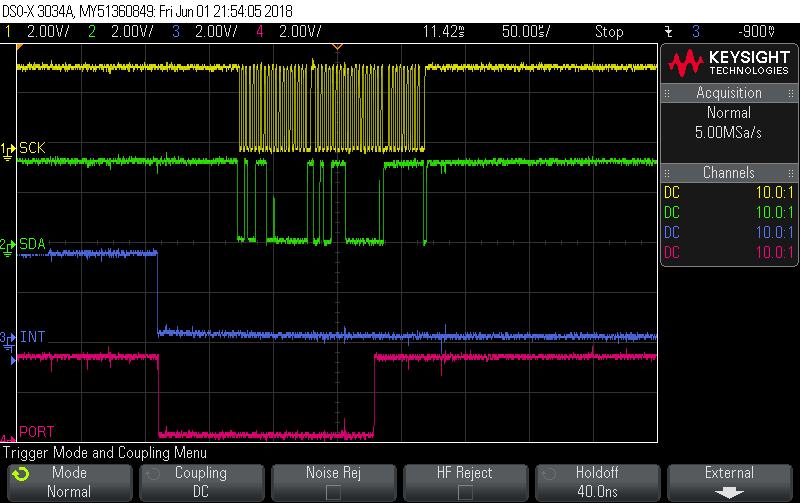

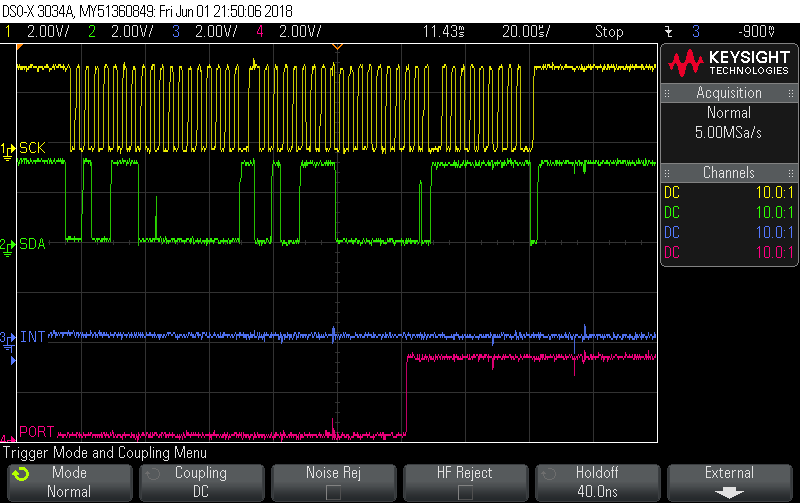

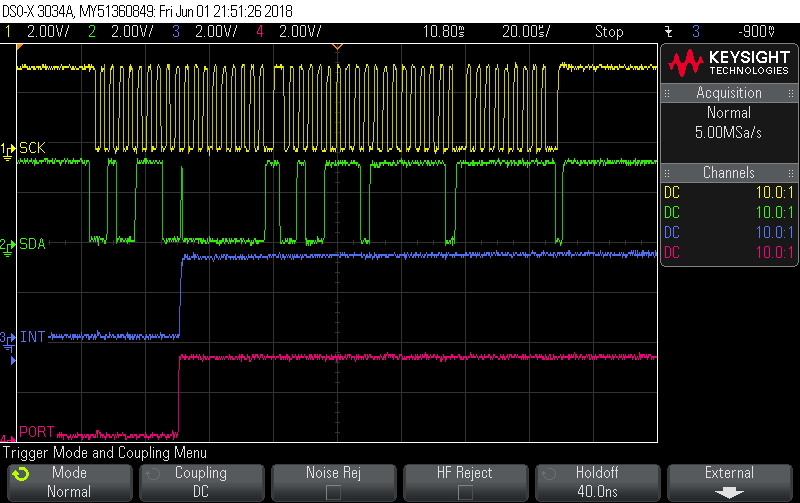

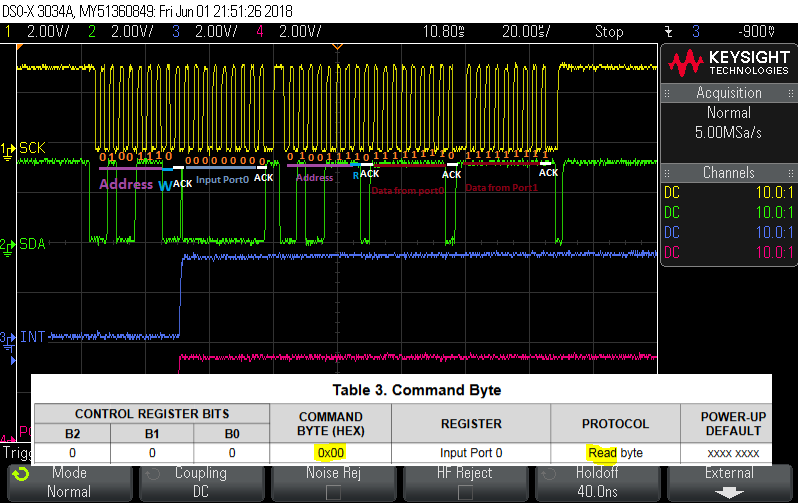

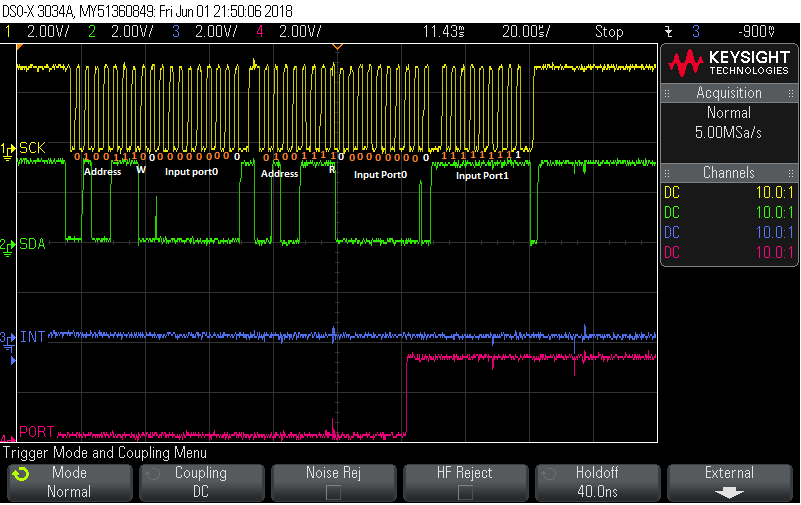

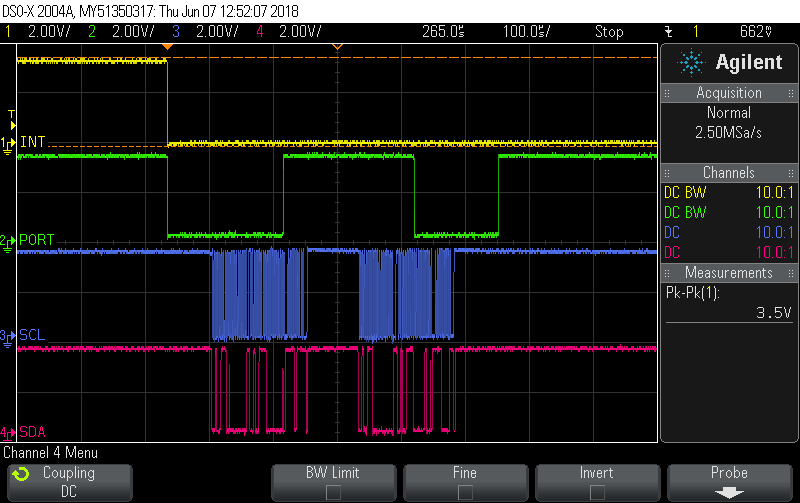

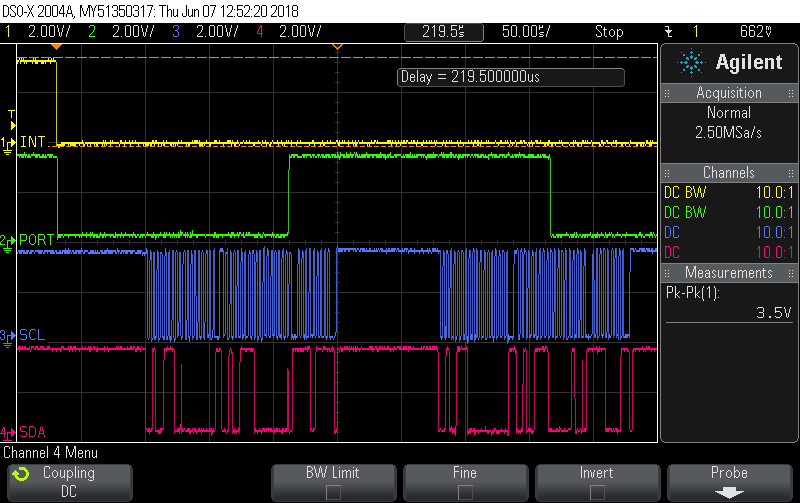

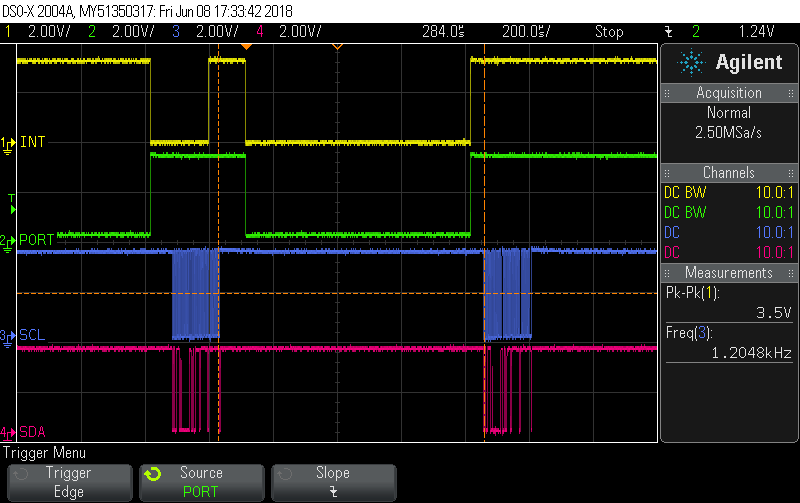

i have configured TCA9555 port 0 as input and port 1 the first 4 pins configured as input and rest of the pins configured as output. TCA9555 is used along with TM4C292NCPDT for input operation. The device is generating the interrupt continuously as long as if we give input in either one of the port making all pins HIGH or LOW. but if we give inputs with combination of two ports over the minute period, its failing to generate the interrupt after either Master reads ports status or port input status changes. the interrupt pin is always de-asserted.

Can anyone suggest what could be the reason for this behavior?

Regards

Bala