Part Number: TCA9545A

Other Parts Discussed in Thread: AM5718, LM63LM64LM96X63EVM, LM96063, PCA9545A

Hi,

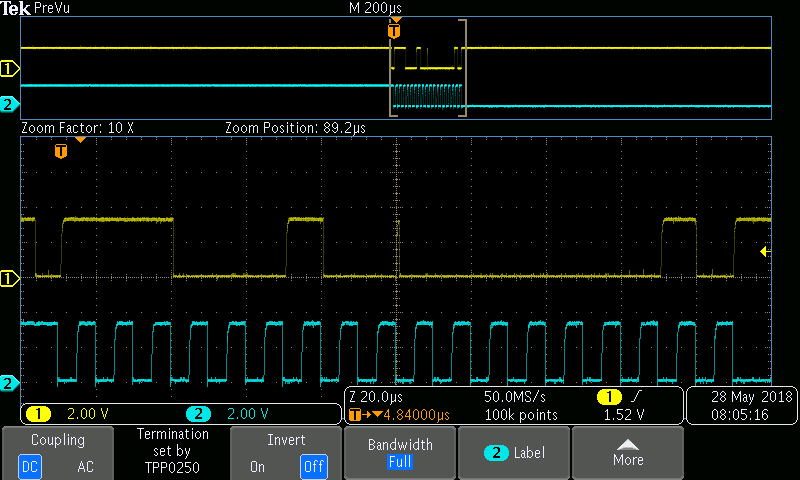

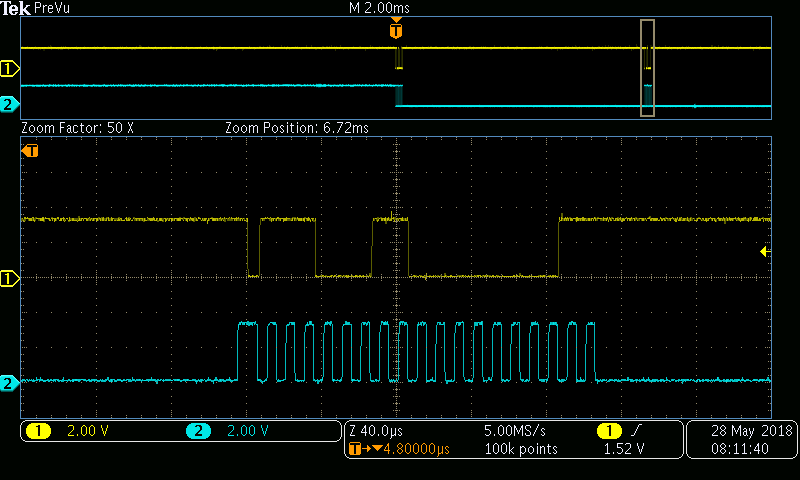

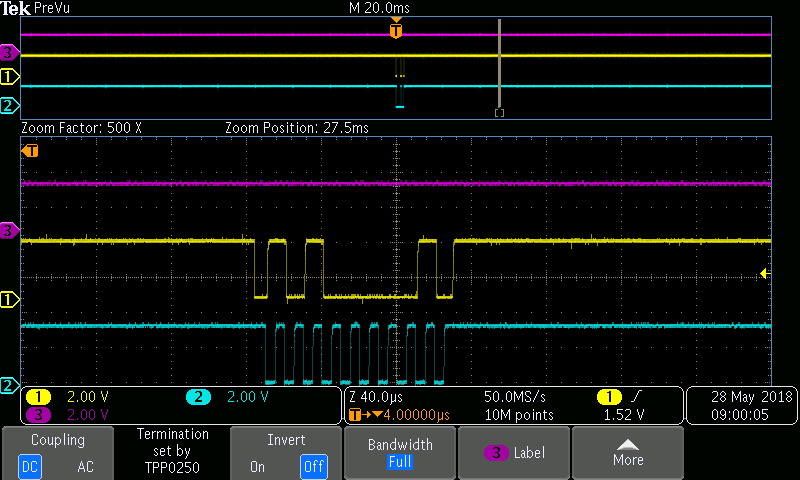

When setting or asking for the active I2C channel the switch responds as expected. However, there is no activity whatsoever on the "channel side" when trying to communicate with devices connected to any of the channels. All channels are stuck at logic high. It's like the pass-gate transistors never turn on and let anything through.

The 2.6 V on the right side should be ok according to the datasheet figure 17 and page 18. I'm not sure about the unused interrupts and unused channels though. Could the pull-up to 3.3 V cause any problems?

Regards

F