Hi Team,

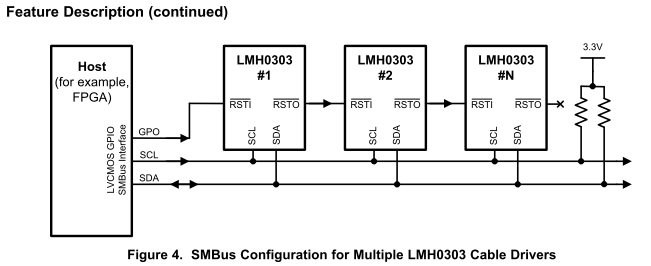

Please allow me to ask you about the Device ID programming for LMH0303, when used with several devices.

Does user needs to insert some wait time between access to LMH0303 #1 and LMH0303 #2, changing Device ID of REG 0x00 ?

I am understanding that LMH0303 has Device ID (Slave address) = 0x2E by default. User would need to use RSTI/RSTO pins to change each Device ID to unique value by writing REG 0x00.

When user Writes REG 0x00 of LMH0303 #1 to a unique Device ID, RSTO output will change to "High" automatically. Then, one could access to the next LMH0303 #2 using Device ID = 0x2E.

There should be some delay from REG 0x00 write and RSTO=high output. Could user keep writing under SMBus clock speed without wait time ?

Best Regards,

Kawai