Part Number: XIO2001

Hi Sirs,

Sorry to bother you.

We are using TI XIO2001 and we found something strange in DMA.

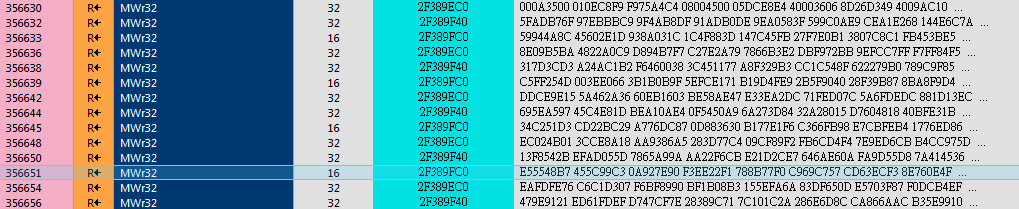

1. When PCI transmit a long single upstream DMA, the transaction could be divided to several PCIe packet with smaller frame size. The address decoded by XIO2001 could be in correct. It’s should be increases instead of below picture :

2. It’s could be no address change when the start address is 32’hxxxx8fc0 with 16Dword size.

The address is allocated by OS and the divided size is decided by XIO2001. It’s seems an address counter overflow phenomenon. How should we do for this issue?

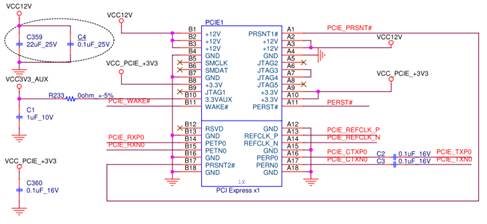

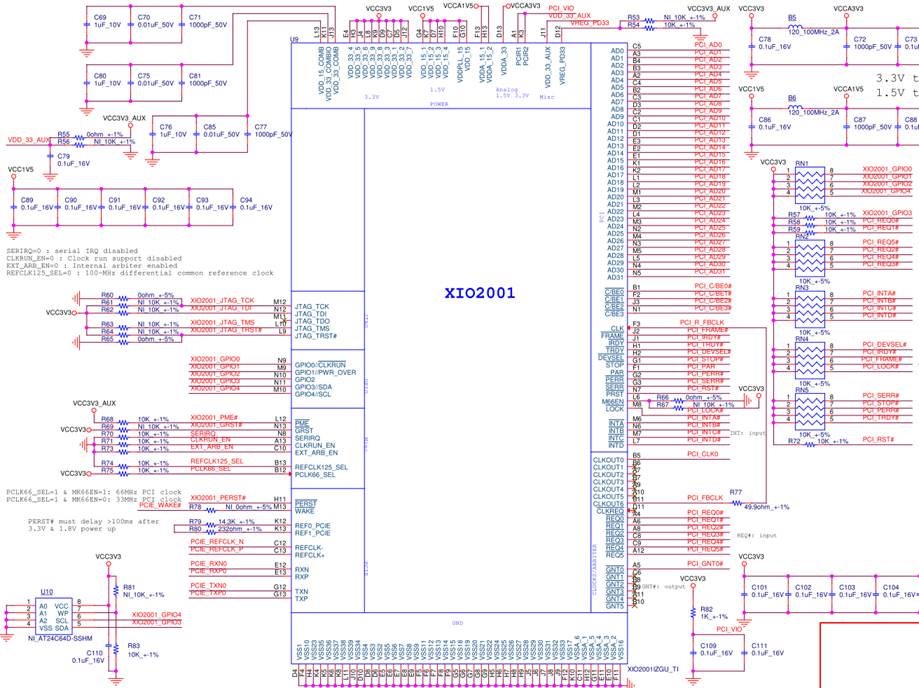

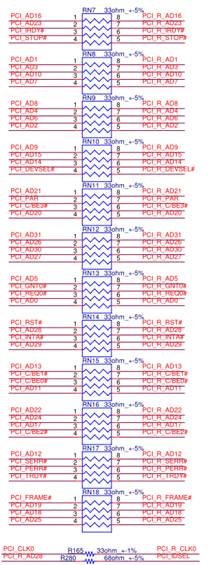

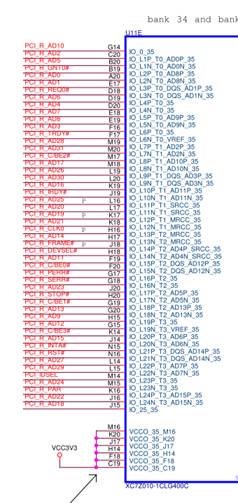

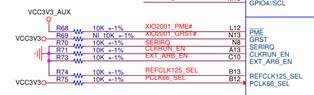

Here’s the schematic for XIO2001