Hi Expert,

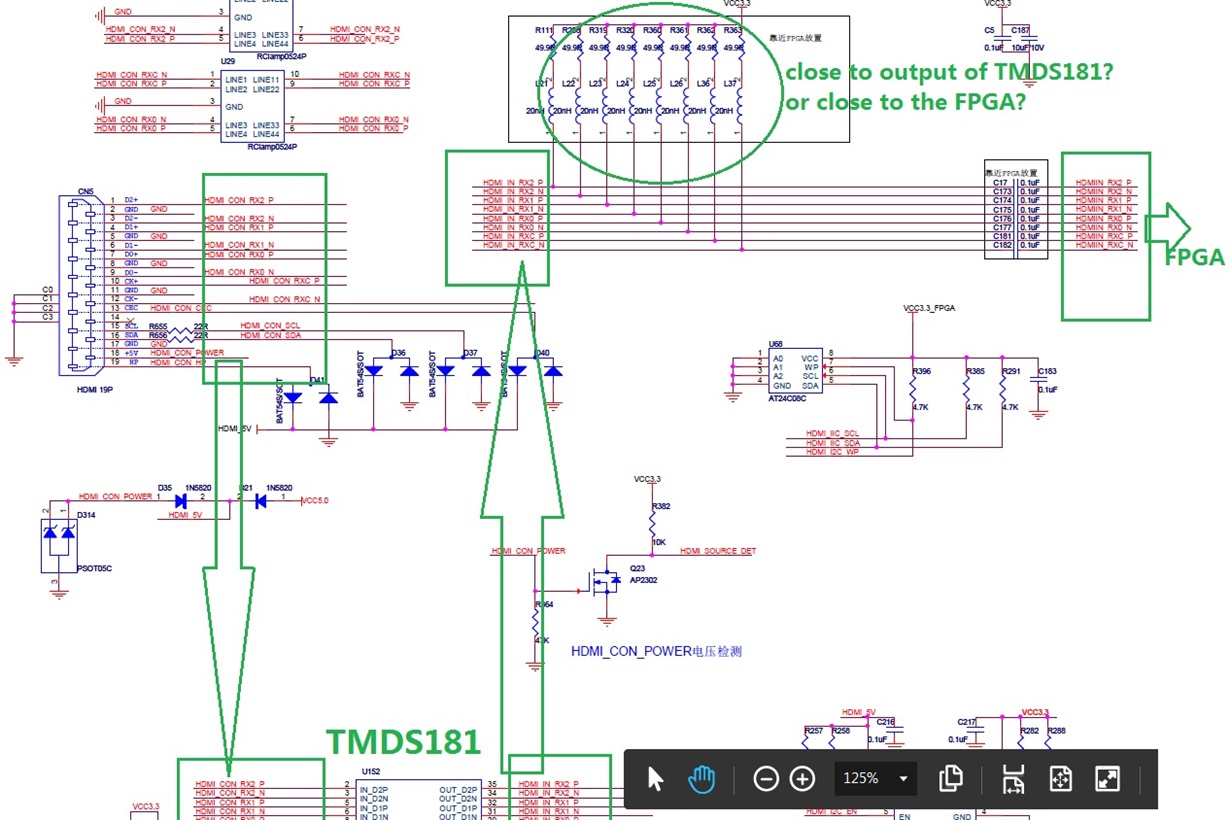

My customer is using the TMDS181 and they are asking a question about the "inductor+resister" network location?

HDMI sink:

HDMI connector => TMDS181 => INDUCTOR + RESISTER NETWORK => FPGA

does INDUCTOR+RESISOTER NETWORK close to the output of TMDS181 or close to the FPGA? why?

Customer's schematic:

Some HDMI sink reference design from the thrid party:

Best Regards

Iven Xu