Other Parts Discussed in Thread: SN65DSI85

I am trying to bring up this part from a Raspberry Pi 3. For now, I'm manually setting the I2C registers

The LVDS test pattern displays correctly using Extclock.

However, the device is not correctly receiving the DSI clock in that the PLL is not locking.

My spectrum analyser shows the clock at 333MHz (my 'scope does not go up that high so it shows as 'fuzz').

The data lane is discernable on my 'scope, exhibting expected sync periods etc.

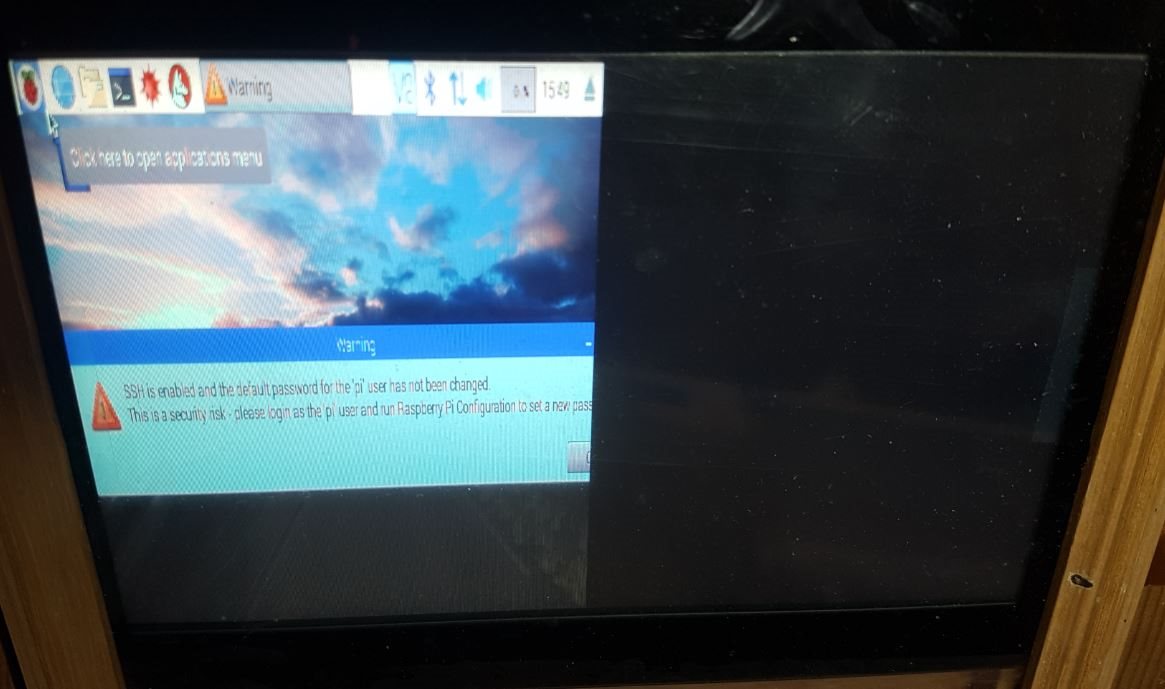

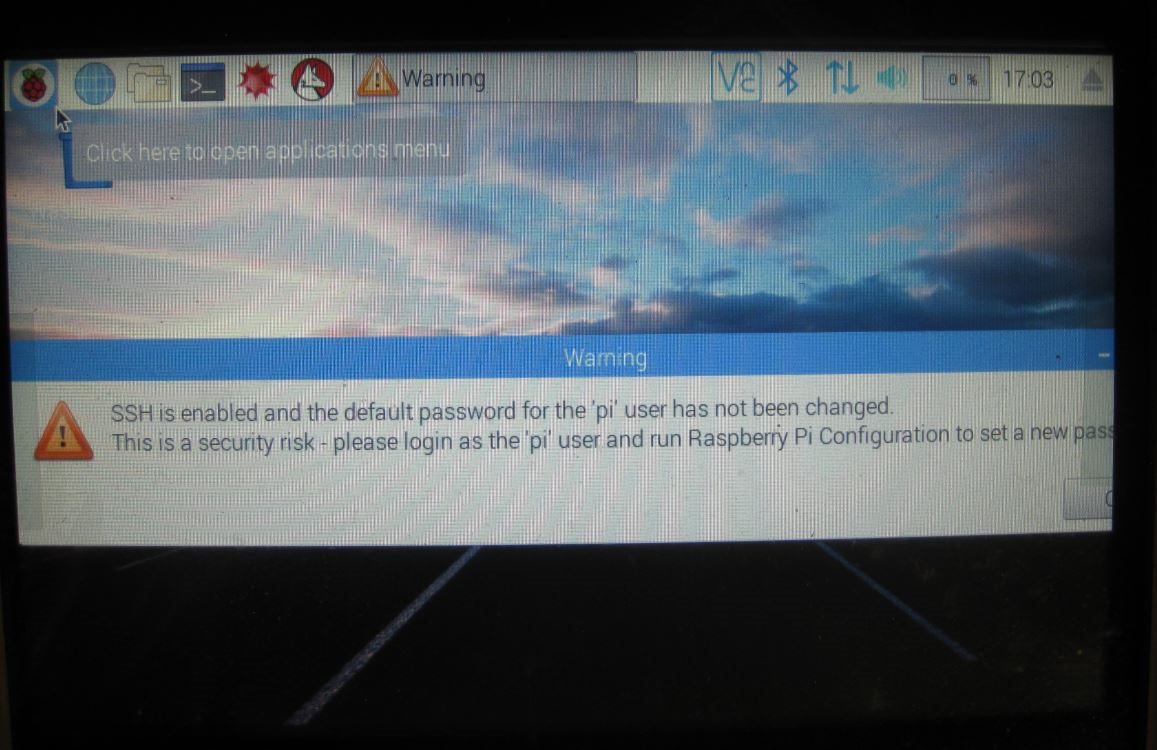

Under the same conditions, the raspberry pi 'official' display is correctly receiving the clock and displaying the image. The ribbon cable connecting the Pi to the display is 6"

The average DC level of the clock (as reprorted by my 100MHz scope) is very low - about 60mV on one leg, and -20mV on the other when connected to the TI chip

When connected to the Tosh chip in the official display, the average DC levels rise to about 170mV

The Tosh datasheet shows that there are registers to control the "Rx Bias resistance" on all the lanes.

Is it the case that one is expected to provide external bias resistors for the DSI Clock input to the Texas chip?