Other Parts Discussed in Thread: DS90UB913A-CXEVM, , DS90UB914A-CXEVM

Hi Team,

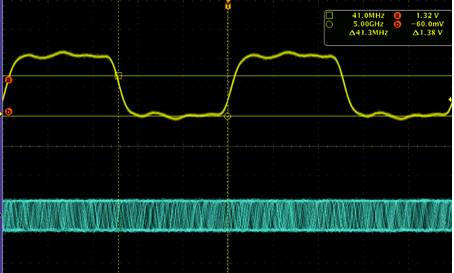

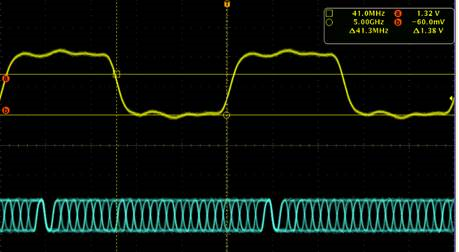

I am evaluating DS90UB913A-CXEVM itself (not connected to Deserializer) and confirmed CML output frequency isn't synchronized with PCLK pin that is connected from pulse generator.

It seems fixed 50MHz internal oscillator is used in this case.

Is it expected behavior?

If the answer is yes, how to synchronize CML output with PCLK pin?

The background of the question is my customer considers to evaluate output waveform quality of his system in PCLK mode without connecting Deserializer.

Best Regards,

Yaita / Japan disty