Hi,

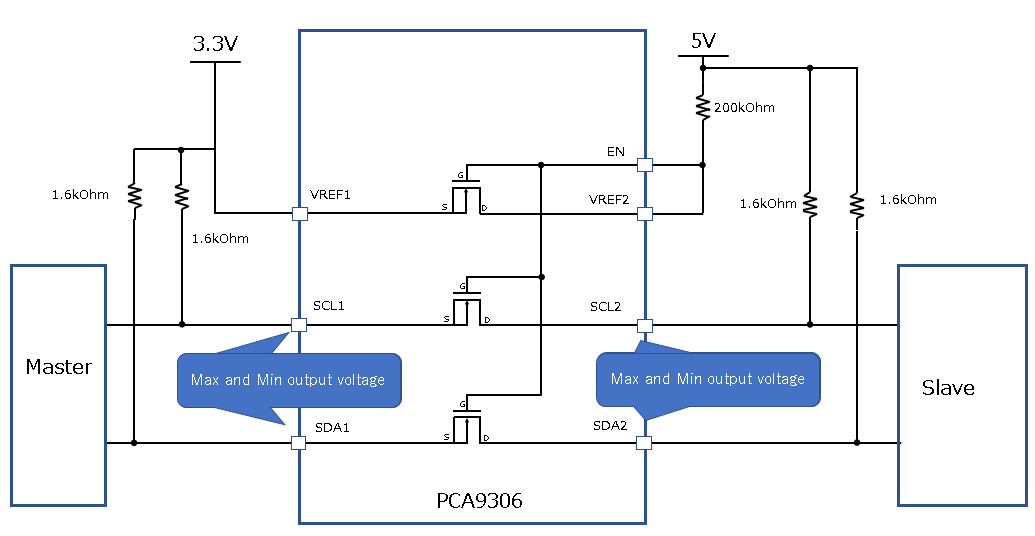

I think of using PCA9306 below circuit.

But Max output voltage and Min aren't defined in datasheet.

Could you let me know Max output voltage and Min output voltage of SCL1/2 and SDA1/2, please?

and could you let me know formula for caluculating this, please?

Best regards,

Shimizu