Hi!

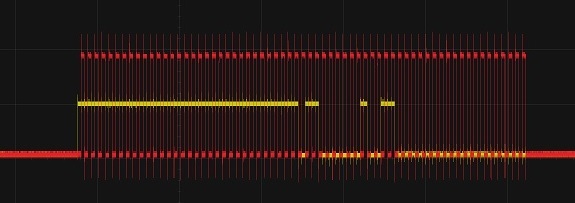

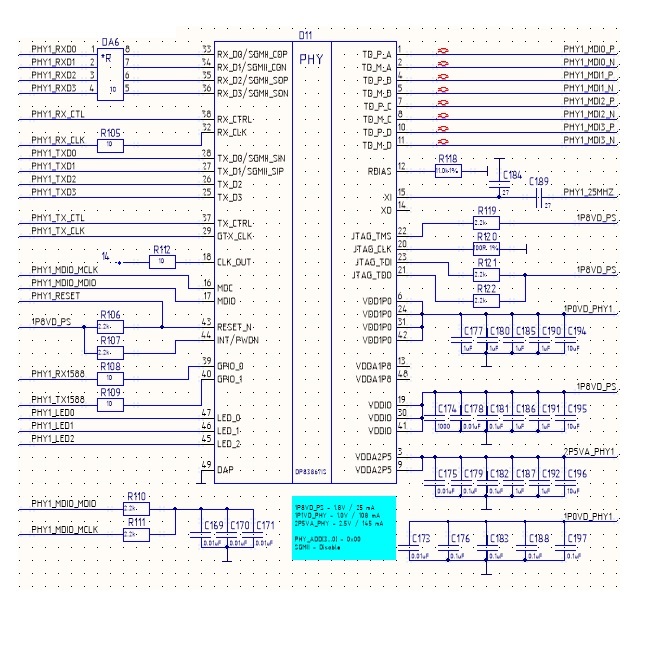

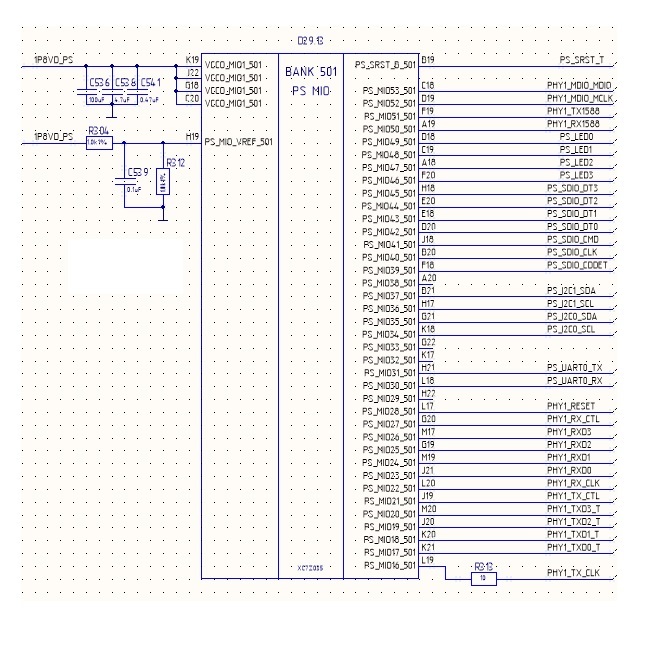

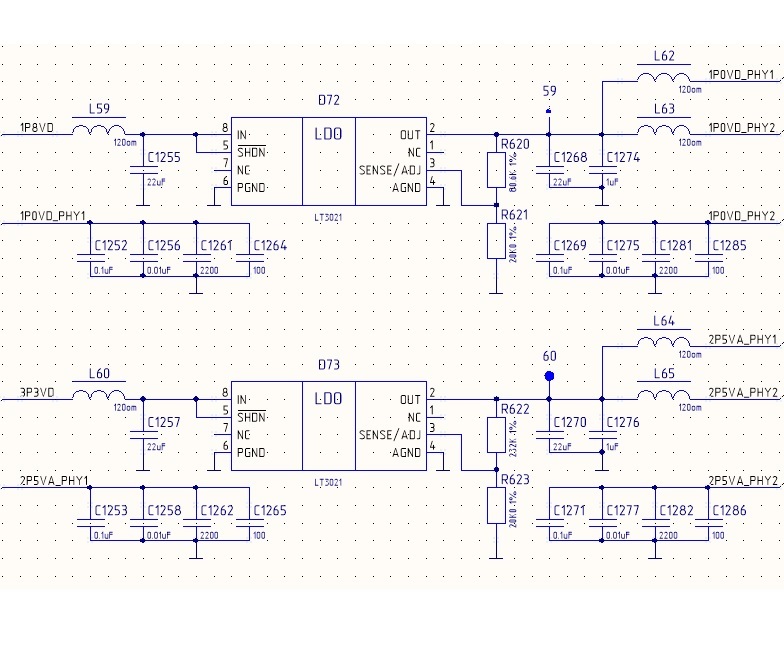

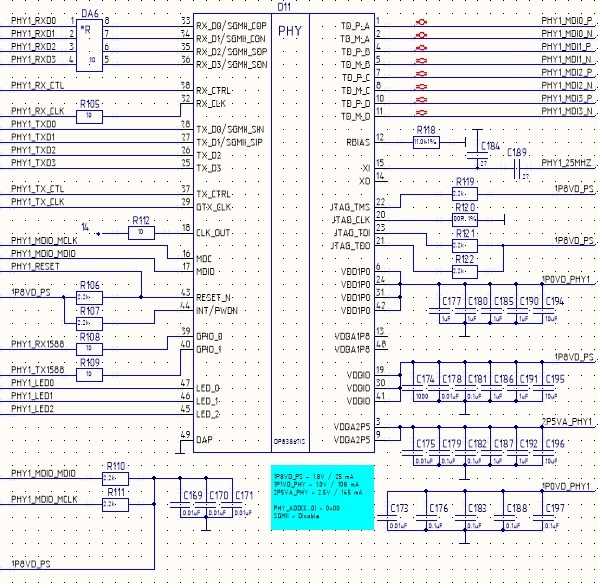

Plese help me. I connect processors system of Zynq-7000 to PHY DP83867IS. Operation mode is RGMII. Power for DP83867IS is tow-supply configuration. The MDIO PHY_ADD configuration is 0x00. MDIO pin have a pullup resistor 2.2 kΩ. When the power is turned on, the MDIO signal is pulled to zero and always reads as zero when reading registers of PHY, but clock is Ok (25MHz). When referring to PHY, the MDIO signal level is ~1.0 V. Then I remove chip PHY signal MDIO is OK.