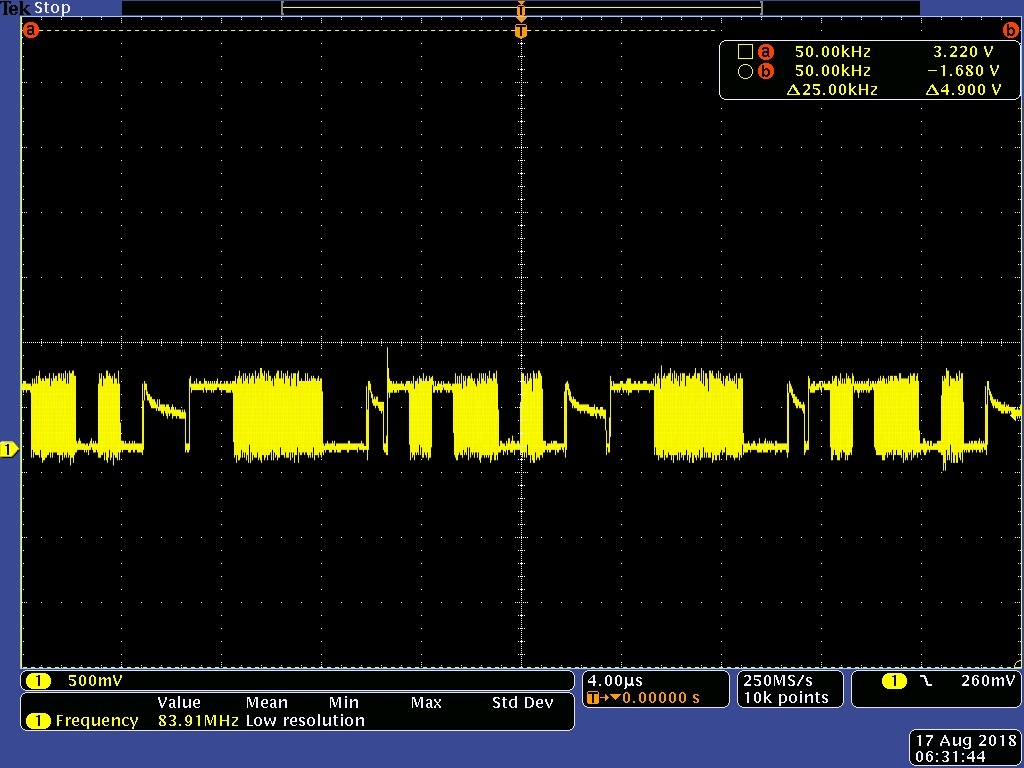

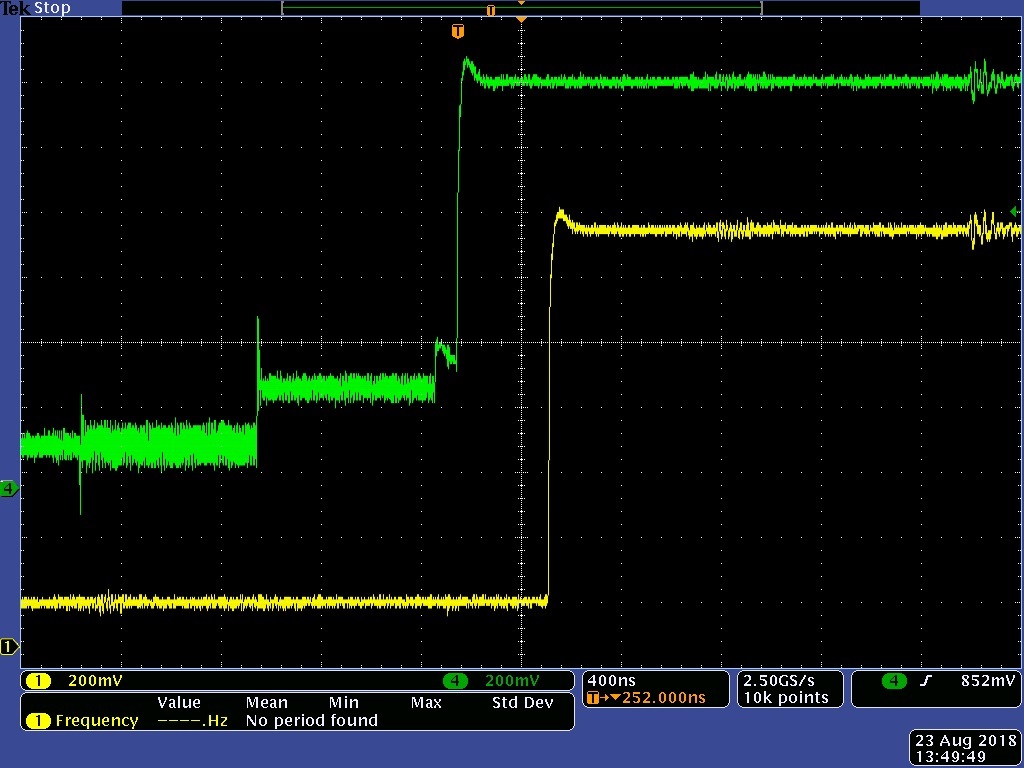

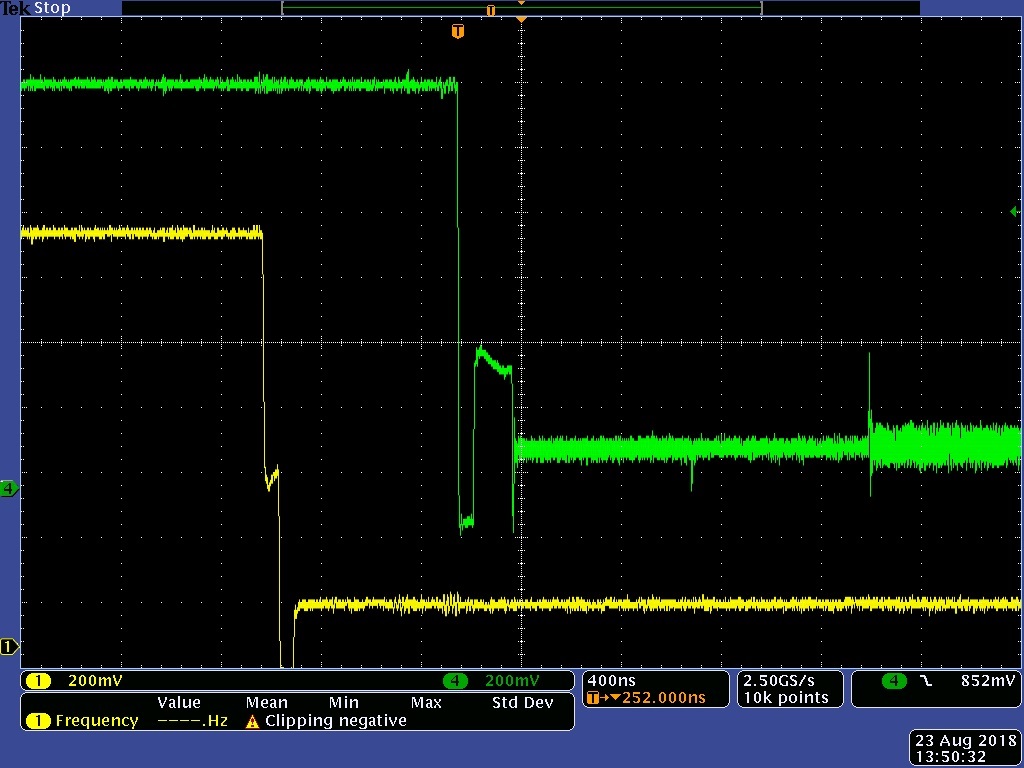

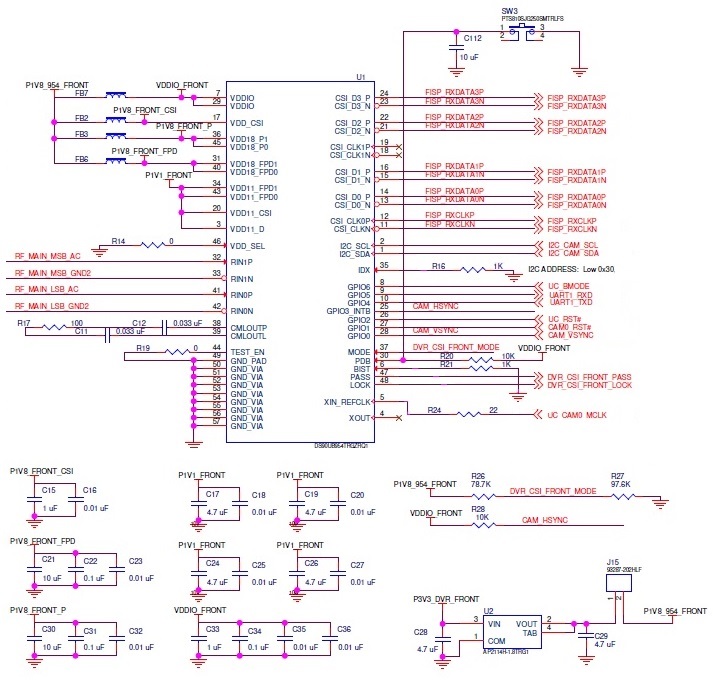

I have a DS90UB954-Q1 down on my board. It is receiving two streams on its' two RX ports. The two streams are synchronized and the 954 is using its' "Line-Interleaved Forwarding" engine to output the data on 4 lanes of its' CSI-2 bus. Everything looks pretty good on the scope except I have no CSI-2 clock. I have been all through the register settings (especially the 0x33 - 0x38 regs) and I cannot find a problem with them. I am setup for continuous clocking. Does anyone have any ideas on what may be happening here?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.