Other Parts Discussed in Thread: TUSB1310

Hello,

How are settle the REFCLKSEL1,0 signals?

In data sheet it seems to have two different ways:

Table 3-8. Strapping Options, the REFCLKSEL1,0 signals come from ULPI_DATA4,5 state value latching at reset release.

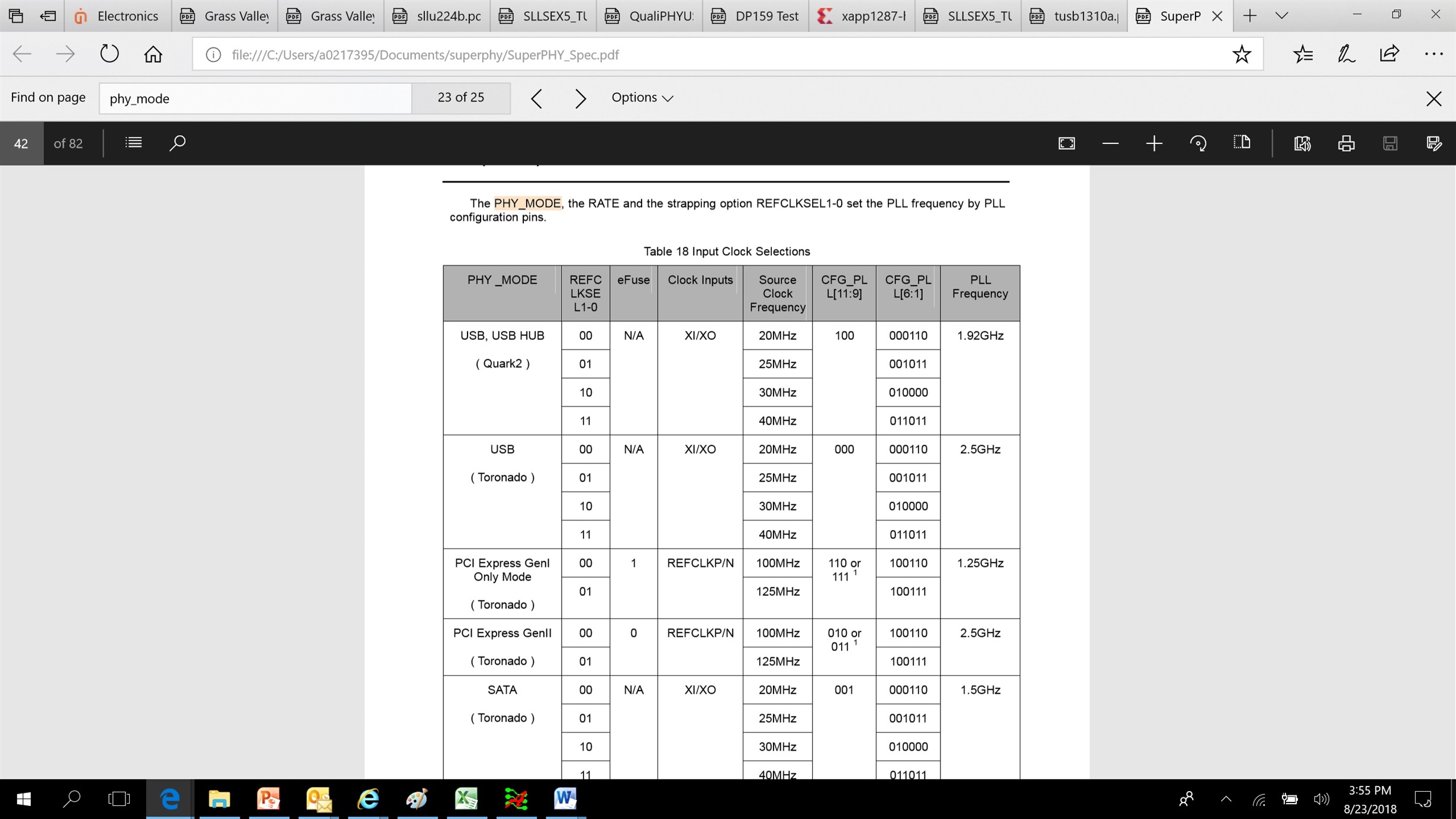

But page 22 it is written "REFCLKSEL1-0 is determined depending on the PHY_MODE pins"

So which one is the good?

Thanks,

Pierre.