Part Number: XIO2001

Hello

I have a question for reset input during power-up.

Usually reset ICs output is undefined (maybe high if it is pulled-up to VDD) when VDD is less than about 0.8V during power-up.

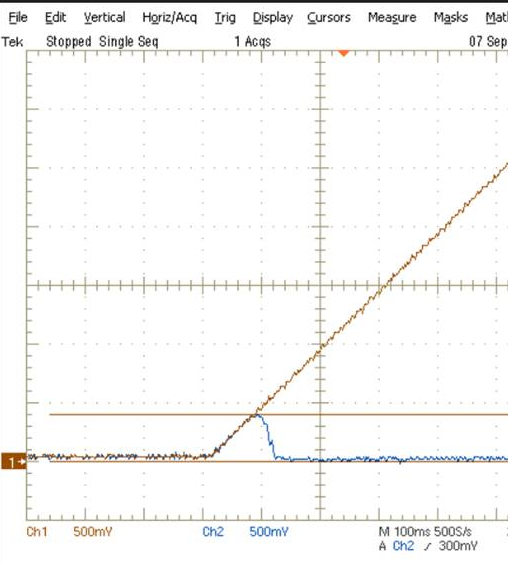

So when using a reset IC to GRST input, during power-up, GRST could be high until VDD reaches at about 0.8V during power-up like the below figure.

My question is that could this kind of glitch for GRST input during power-up initial stage cause any problem?

Regards,

Oba