Part Number: DS90UB954-Q1

Dear Sir,

Customer found sometimes it will occur CSI Error (0x4e bit3 is set) after power cycle initial UB953/UB954.

It will let host side cannot receive frame.

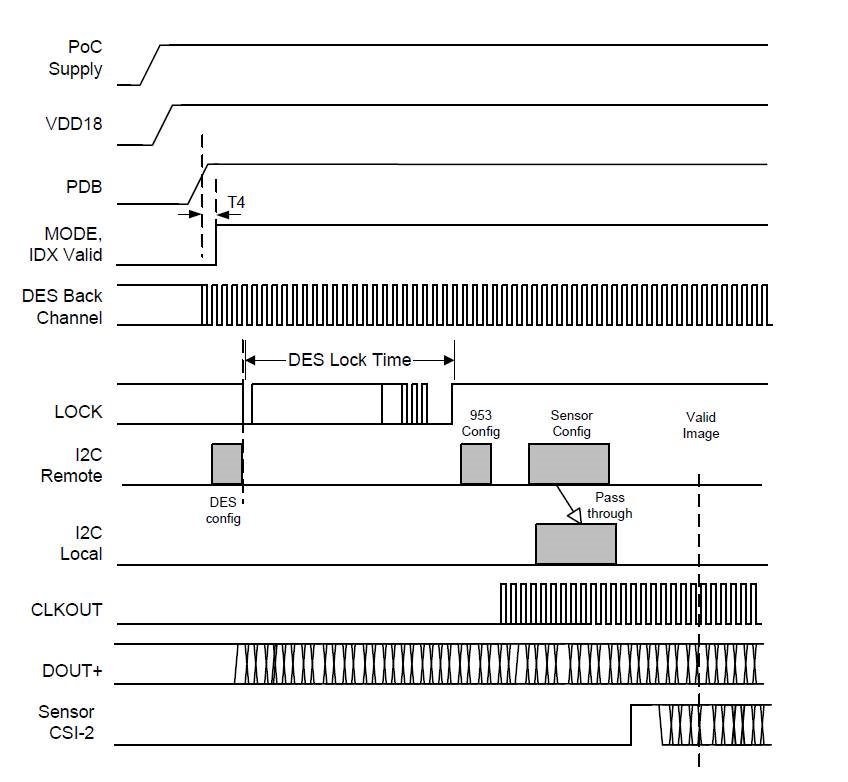

We checked UB953 spec. about power sequence, it need wait for "DEC LOCK TIME" between initial UB954 and initial UB953.

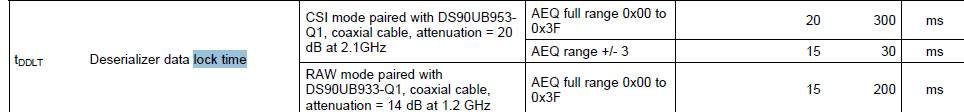

We checked with d/s for lock time(tDDLT), the max. will be 300ms

Customer try implement lock time(tDDLT)=300mS found the issue will gone.

But their end-customer has spec. for initial serdes duration need <=64ms.

Pls advise how we can do for satisfied no issue and duration<=64ms?

Thanks, Ian.