Hello all,

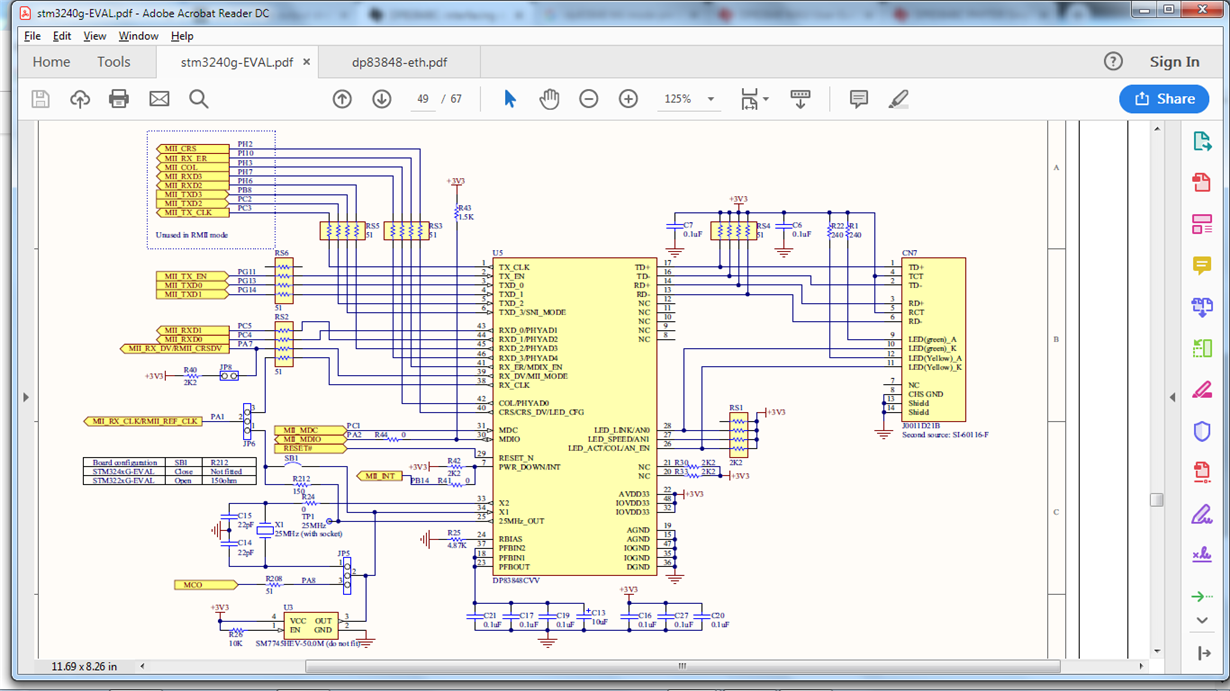

i am using stm3240g-eval development board and together with dp83848C and I am trying to bring up the Ethernet module.

I was unable to send and receive data using the MII interface.

the following configurations has been set.

MII mode

PHY address - 0x01

Auto.negotiation - Enabled

speed - 100Mbps

with above configuration, in basic mode status register bit 5 is not set.

is there any internal clock of 25MHZ to the dp83848C??.

Kindly help me overcome the above problems.

Best Regards,

Siva