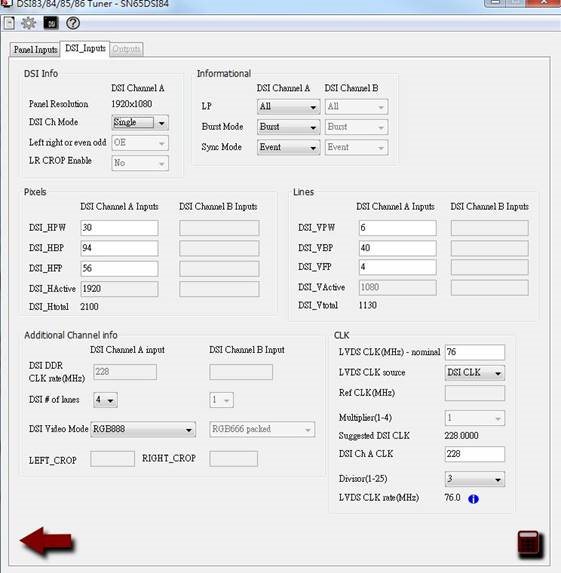

Part Number: SN65DSI84

Other Parts Discussed in Thread: DSI-TUNER

Dear Sir,

Our customer is using SN65DSI84 and encounter a problem.

The display color is not as expected.

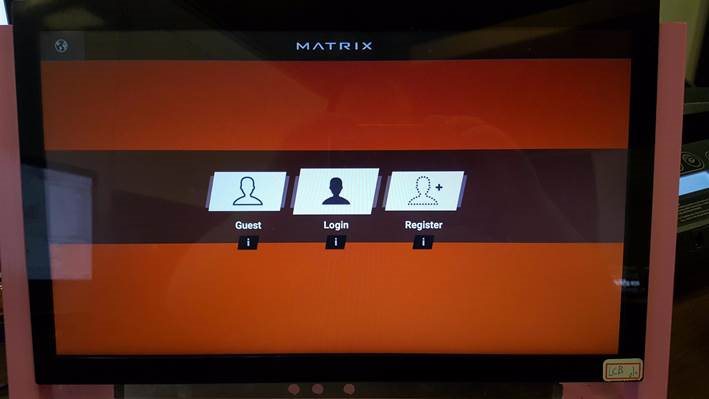

This is the original picture:

But the display show as below:

Do you have any experience about it?

Can we set registers to modify it?

Or it should be tuned by video source?

Thank you very much