Part Number: TLK10232

Hi,

For a new project, i use a TLK10232 for 10Gb link.

The high speed side need to comunicate at 10.312Gb and Low speed at 3.125Gb.

In my schematic :

1/ MODE_SEL = ST = '0' (pull down 4.7K) for 10GBASE-KR mode.

2/ Refclk0 = refclk1 = 156.25MHz (refclk1 is only present in case of future problem but only refclk0 will be used).

3/ All channel A & B will be used at the same frame rate HS & LS side.

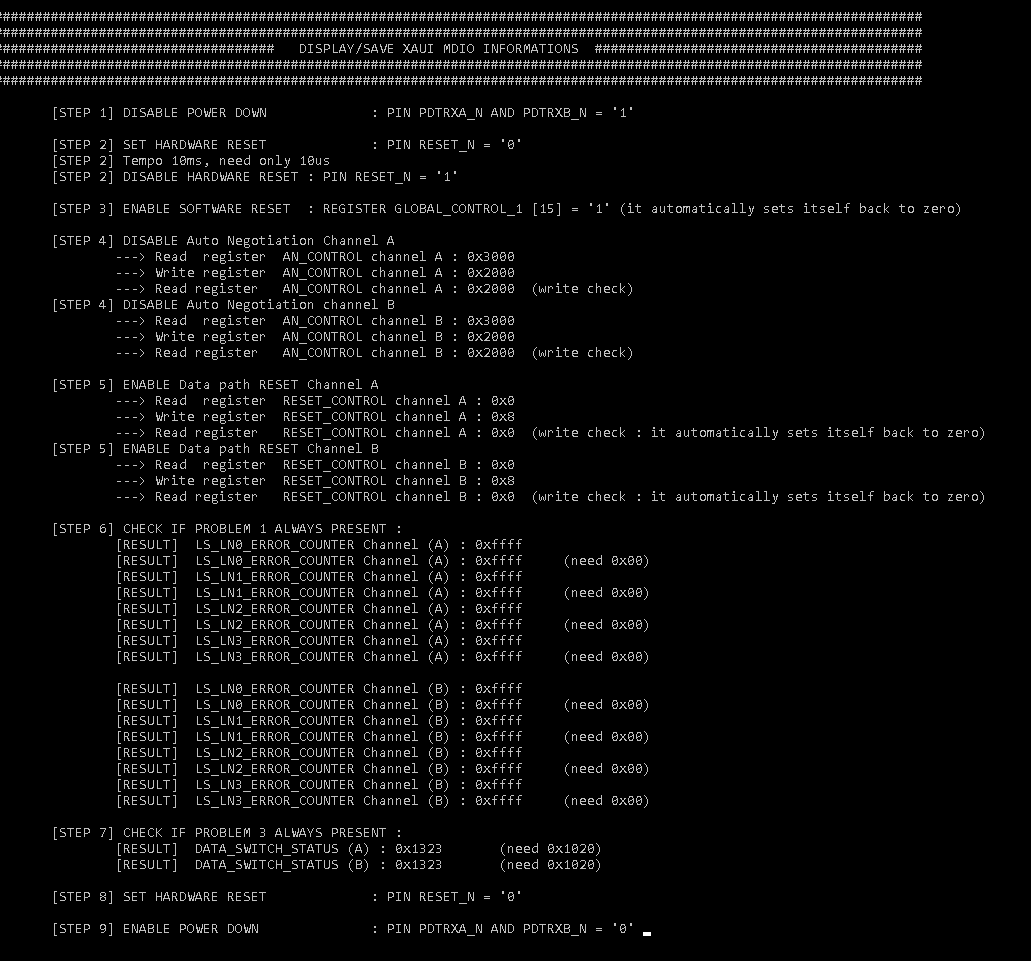

I developed a communication interface with MDIO.This interface works well. I can read or write all registers but i have 3 problems. The 3 problems appear on CHANNEL A and B.

In my software application, il only pass PDTRXA_N and PDTRXB_N to high level (initialized at low level) . And after i read all registers (without any initialization or modification before).

All values can be see in XAUI_MDIO_REGISTER_CHANNELA2.txt

###################################################################################### ###################### Vendor Specific Device Registers ######################## ###################################################################################### REGISTER GLOBAL_CONTROL_1 : 0x610 REGISTER CHANNEL_CONTROL_1 : 0xb24 (need 0x0b00) ti use only REGISTER HS_SERDES_CONTROL_1 : 0x831d REGISTER HS_SERDES_CONTROL_2 : 0xa848 REGISTER HS_SERDES_CONTROL_3 : 0x1500 REGISTER HS_SERDES_CONTROL_4 : 0x2000 REGISTER LS_SERDES_CONTROL_1 : 0xf115 REGISTER LS_SERDES_CONTROL_2 : 0x0 (need 0xDC04) REGISTER LS_SERDES_CONTROL_3 : 0x0 (need 0x000d) ti use only REGISTER HS_OVERLAY_CONTROL : 0x380 REGISTER LS_OVERLAY_CONTROL : 0x4000 REGISTER LOOPBACK_TP_CONTROL : 0xd10 REGISTER LS_CONFIG_CONTROL : 0x371 (need 0x0330) ti use only REGISTER CLK_CONTROL : 0x2f80 REGISTER RESET_CONTROL : 0x0 REGISTER CHANNEL_STATUS_1 : 0x2000 (need 0x0000) loss of signal indicator @ '1' REGISTER HS_ERROR_COUNTER : 0xfffd REGISTER LS_LN0_ERROR_COUNTER : 0xfffd REGISTER LS_LN1_ERROR_COUNTER : 0xfffd REGISTER LS_LN2_ERROR_COUNTER : 0xfffd REGISTER LS_LN3_ERROR_COUNTER : 0xfffd REGISTER LS_STATUS_1 : 0x8404 (need 0x0000) LS Invalid decode error for selected lane. REGISTER HS_STATUS_1 : 0xc000 (need 0x0000) ti use only REGISTER DST_CONTROL_1 : 0x2000 REGISTER DST_CONTROL_2 : 0xc20 REGISTER DSR_CONTROL_1 : 0x2500 REGISTER DSR_CONTROL_2 : 0x4c20 REGISTER DATA_SWITCH_STATUS : 0x0 (need 0x1020) no coherent bit 15 REGISTER LS_CH_CONTROL_1 : 0x0 REGISTER HS_CH_CONTROL_1 : 0x0 REGISTER EXT_ADDRESS_CONTROL : 0x0 REGISTER EXT_ADDRESS_DATA : 0x0 REGISTER VS_10G_LN_ALIGN_ACODE_P : 0x283 REGISTER VS_10G_LN_ALIGN_ACODE_N : 0x17c REGISTER MC_AUTO_CONTROL : 0xf REGISTER DST_ON_CHAR_CONTROL : 0x2fd REGISTER DST_OFF_CHAR_CONTROL : 0x2fd REGISTER DST_STUFF_CHAR_CONTROL : 0x207 REGISTER DSR_ON_CHAR_CONTROL : 0x2fd REGISTER DSR_OFF_CHAR_CONTROL : 0x2fd REGISTER DSR_STUFF_CHAR_CONTROL : 0x207 REGISTER LATENCY_MEASURE_CONTROL : 0x0 REGISTER LATENCY_COUNTER_2 : 0x0 REGISTER LATENCY_COUNTER_1 : 0x0 REGISTER TRIGGER_LOAD_CONTROL : 0x0 REGISTER TRIGGER_EN_CONTROL : 0x0 ###################################################################################### ########################### PMA/PMD Registers ################################## ###################################################################################### REGISTER PMA_CONTROL_1 : 0x0 REGISTER PMA_STATUS_1 : 0x2 REGISTER PMA_DEV_IDENTIFIER_1 : 0x4000 REGISTER PMA_DEV_IDENTIFIER_2 : 0x5100 REGISTER PMA_SPEED_ABILITY : 0x11 REGISTER PMA_DEV_PACKAGE_1 : 0xb REGISTER PMA_DEV_PACKAGE_2 : 0x4000 REGISTER PMA_STATUS_2 : 0xb000 REGISTER PMA_RX_SIGNAL_DET_STATUS : 0x0 REGISTER PMA_EXTENDED_ABILITY : 0x50 REGISTER LT_TRAIN_CONTROL : 0x2 REGISTER LT_TRAIN_STATUS : 0x0 REGISTER LT_LINK_PARTNER_CONTROL : 0x0 REGISTER LT_LINK_PARTNER_STATUS : 0x0 REGISTER LT_LOCAL_DEVICE_CONTROL : 0x0 REGISTER LT_LOCAL_DEVICE_STATUS : 0x0 REGISTER KX_STATUS : 0x3000 REGISTER KR_FEC_ABILITY : 0x3 REGISTER KR_FEC_CONTROL : 0x0 REGISTER KR_FEC_C_COUNT_1 : 0x0 REGISTER KR_FEC_C_COUNT_2 : 0x0 REGISTER KR_FEC_UC_COUNT_1 : 0x0 REGISTER KR_FEC_UC_COUNT_2 : 0x0 REGISTER KR_VS_FIFO_CONTROL_1 : 0xcc4c REGISTER KR_VS_TP_GEN_CONTROL : 0x0 REGISTER KR_VS_TP_VER_CONTROL : 0x0 REGISTER KR_VS_CTC_ERR_CODE_LN0 : 0xce00 REGISTER KR_VS_CTC_ERR_CODE_LN1 : 0x0 REGISTER KR_VS_CTC_ERR_CODE_LN2 : 0x0 REGISTER KR_VS_CTC_ERR_CODE_LN3 : 0x80 REGISTER KR_VS_LN0_EOP_ERROR_COUNTER : 0xfffd REGISTER KR_VS_LN1_EOP_ERROR_COUNTER : 0xfffd REGISTER KR_VS_LN2_EOP_ERROR_COUNTER : 0xfffd REGISTER KR_VS_LN3_EOP_ERROR_COUNTER : 0xfffd REGISTER KR_VS_TX_CTC_DROP_COUNT : 0xfffd REGISTER KR_VS_TX_CTC_INSERT_COUNT : 0xfffd REGISTER KR_VS_RX_CTC_DROP_COUNT : 0xfffd REGISTER KR_VS_RX_CTC_INSERT_COUNT : 0xfffd REGISTER KR_VS_STATUS_1 : 0x0 REGISTER KR_VS_TX_CRCJ_ERR_COUNT_1 : 0xffff (need 0xfffd) error REGISTER KR_VS_TX_CRCJ_ERR_COUNT_2 : 0xffff (need 0xfffd) error REGISTER KR_VS_TX_LN0_HLM_ERR_COUNT : 0xffff (need 0xfffd) error REGISTER KR_VS_TX_LN1_HLM_ERR_COUNT : 0xffff (need 0xfffd) error REGISTER KR_VS_TX_LN2_HLM_ERR_COUNT : 0xffff (need 0xfffd) error REGISTER KR_VS_TX_LN3_HLM_ERR_COUNT : 0xffff (need 0xfffd) error REGISTER LT_VS_CONTROL_2 : 0x200 (need 0x0000) ti use only ###################################################################################### ############################# PCS Registers ############################### ###################################################################################### REGISTER PCS_CONTROL : 0x0 REGISTER PCS_STATUS_1 : 0x2 REGISTER PCS_STATUS_2 : 0x8001 REGISTER KR_PCS_STATUS_1 : 0x4 REGISTER KR_PCS_STATUS_2 : 0x0 REGISTER PCS_TP_SEED_A0 : 0x0 REGISTER PCS_TP_SEED_A1 : 0x0 REGISTER PCS_TP_SEED_A2 : 0x0 REGISTER PCS_TP_SEED_A3 : 0x0 REGISTER PCS_TP_SEED_B0 : 0x0 REGISTER PCS_TP_SEED_B1 : 0x0 REGISTER PCS_TP_SEED_B2 : 0x0 REGISTER CS_TP_SEED_B3 : 0x0 REGISTER PCS_TP_CONTROL : 0x0 REGISTER PCS_TP_ERR_COUNT : 0x0 REGISTER PCS_VS_CONTROL : 0xb0 REGISTER PCS_VS_STATUS : 0xfd ###################################################################################### ####################### Auto-Negotiation Registers ############################### ###################################################################################### REGISTER AN_CONTROL : 0x3000 REGISTER AN_STATUS : 0x88 REGISTER AN_DEV_PACKAGE : 0x80 REGISTER AN_ADVERTISEMENT_1 : 0x1001 REGISTER AN_ADVERTISEMENT_2 : 0x80 REGISTER AN_ADVERTISEMENT_3 : 0x4000 REGISTER AN_LP_ADVERTISEMENT_1 : 0x1 REGISTER AN_LP_ADVERTISEMENT_2 : 0x0 REGISTER AN_LP_ADVERTISEMENT_3 : 0x0 REGISTER AN_XNP_TRANSMIT_1 : 0x2000 REGISTER AN_XNP_TRANSMIT_2 : 0x0 REGISTER AN_XNP_TRANSMIT_3 : 0x0 REGISTER AN_LP_XNP_ABILITY_1 : 0x0 REGISTER AN_LP_XNP_ABILITY_2 : 0x0 REGISTER AN_LP_XNP_ABILITY_3 : 0x0 REGISTER AN_BP_STATUS : 0x1

PROBLEM 1 :

Some COR (Clear-On-Read) Register never pass to '0' when I read it.

For example LS_LN0_ERROR_COUNTER, LS_LN1_ERROR_COUNTER, LS_LN2_ERROR_COUNTER and LS_LN3_ERROR_COUNTER.

I don't try to test all COR Registers but these 4 registers never pass to 0 when i read it. I saw this problem when i tried to use test pattern.

Each time i read it value = default register = 0xFFFD.

PROBLEM 2 :

It's the biggest problem because i cannot use LS side.

Register LS_SERDES_CONTROL_2 always equal to 0. I tried to write this register to default value 0xDC04 but when i read it again, value = 0.

I cannot change this register. In datasheet we can read that this register depend on PD_TRXx_N and LS_TX_ENRX register bit 1E.0001 bit 15.

In my configuration PD_TRXx_N = '1' (hardware check) and LS_TX_ENRX register bit 1E.0001 bit 15 = '0' (Can be checked in .txt file).

PROBLEM 3 : .

DATA_SWITCH_STATUS value = 0. Default value is 0x1020.

Here it's impossible to have bit [15:12] = 0000 because it's not a possible value in datasheet. It's Read Only register so i cannot try to fixe this value.

If someone can help me?

Thanks.