Other Parts Discussed in Thread: DS125BR401

Dear Team,

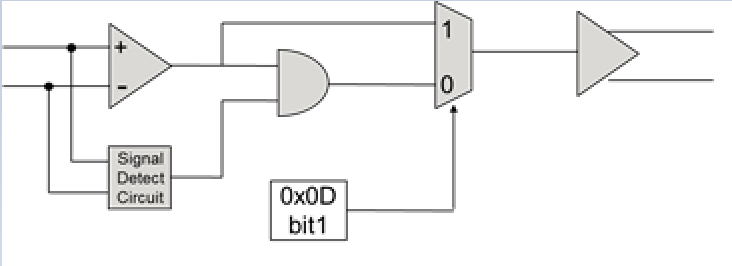

My customer has a detection issue when connecting to a specific SAS HDD.

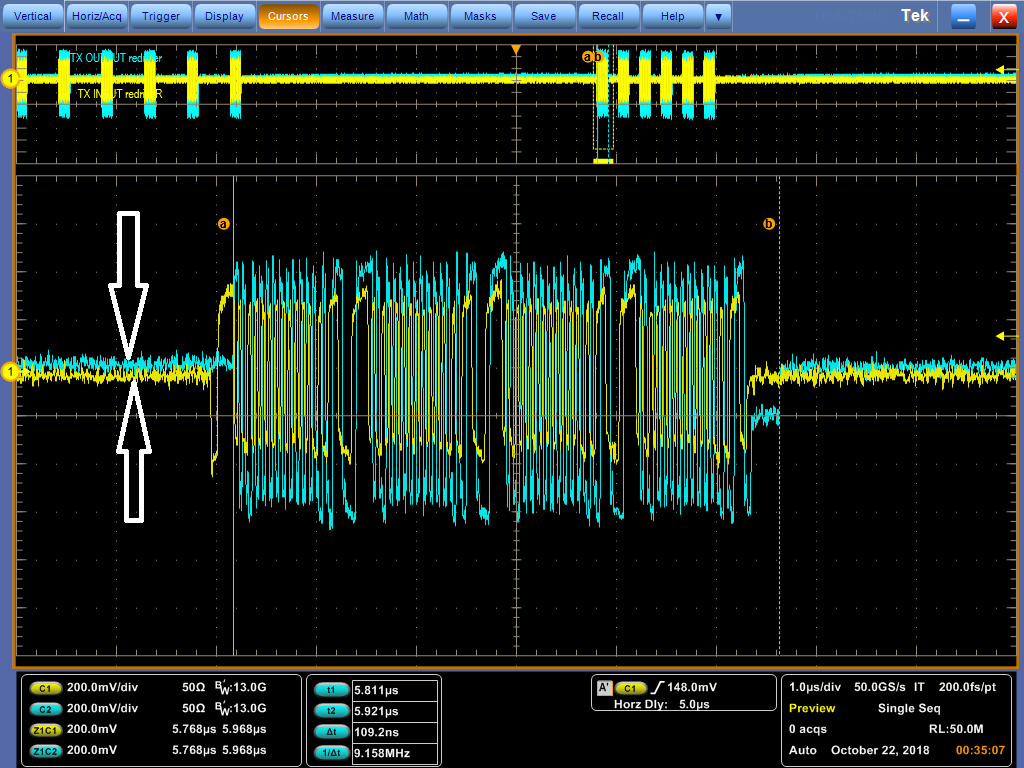

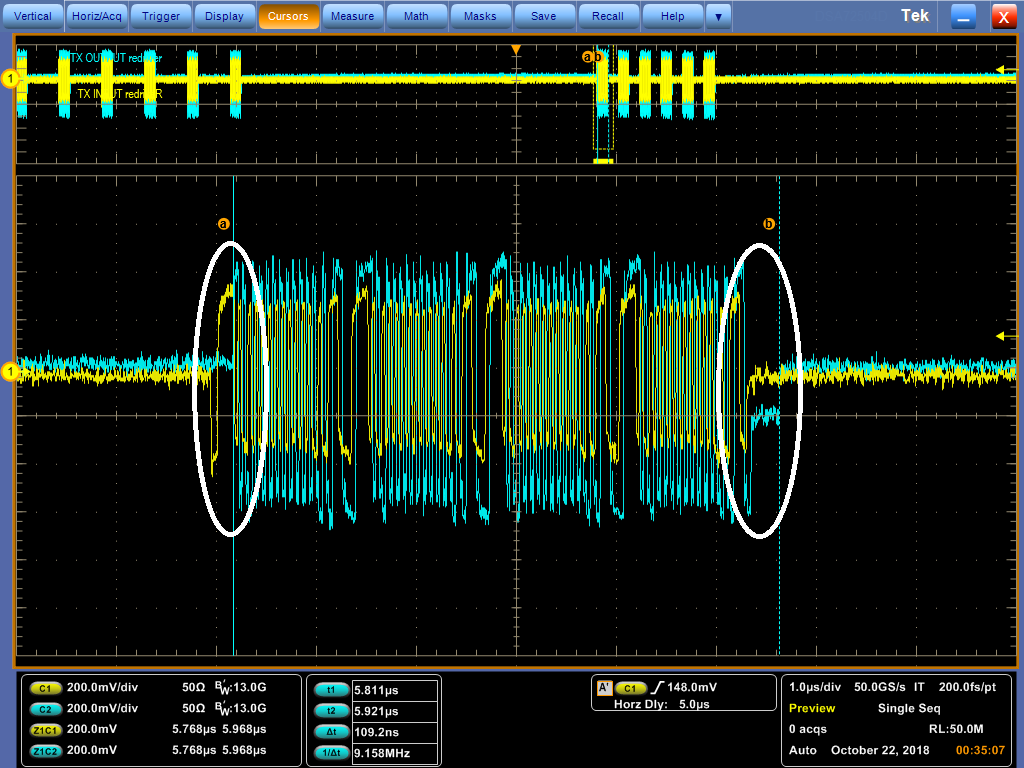

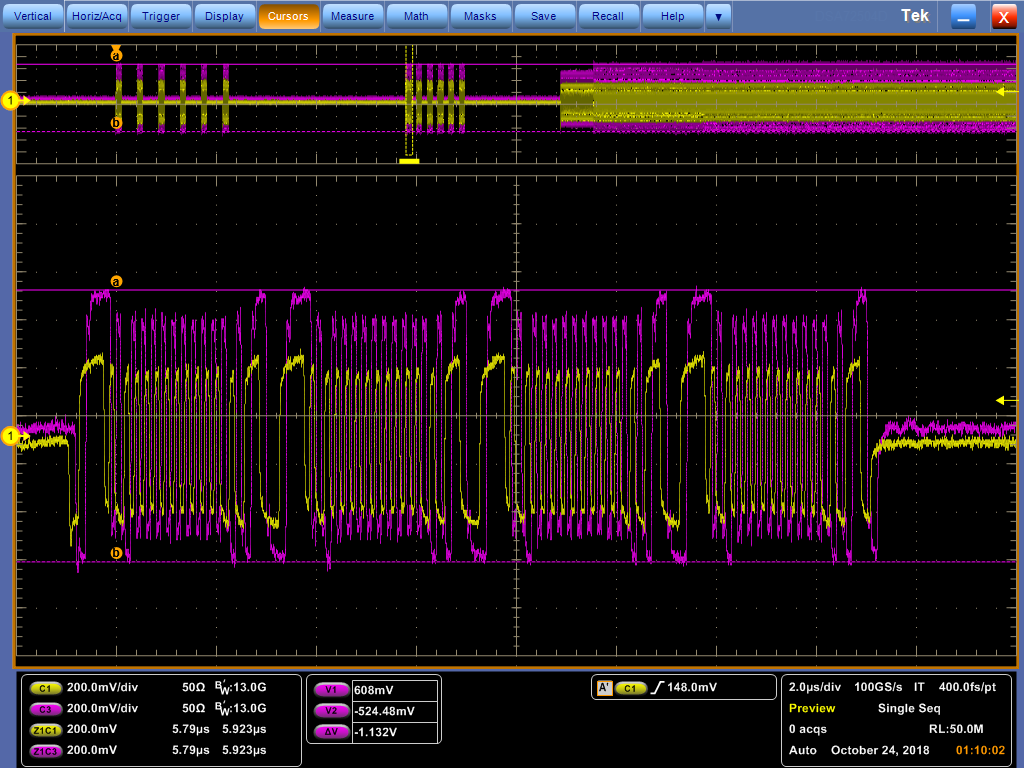

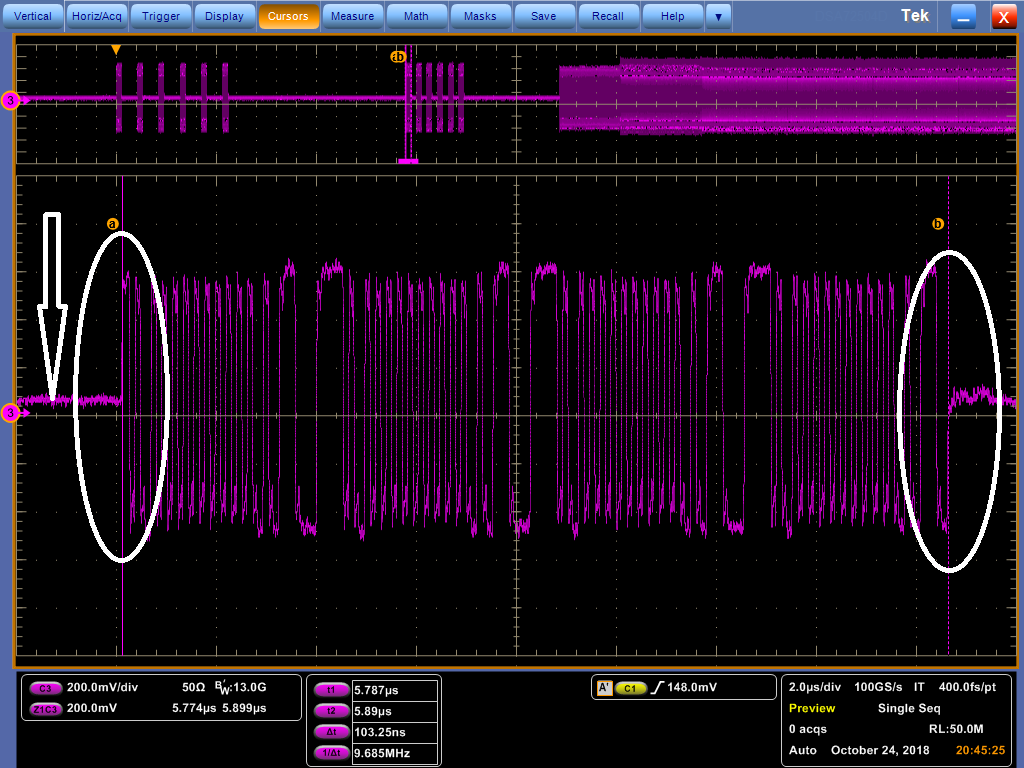

And they found that OOB signal of input side is different from the output side.

So we would like to know the reason why OOB signal are not the same. Please help to comment.

Is there any register that can adjust the signal detection signal?

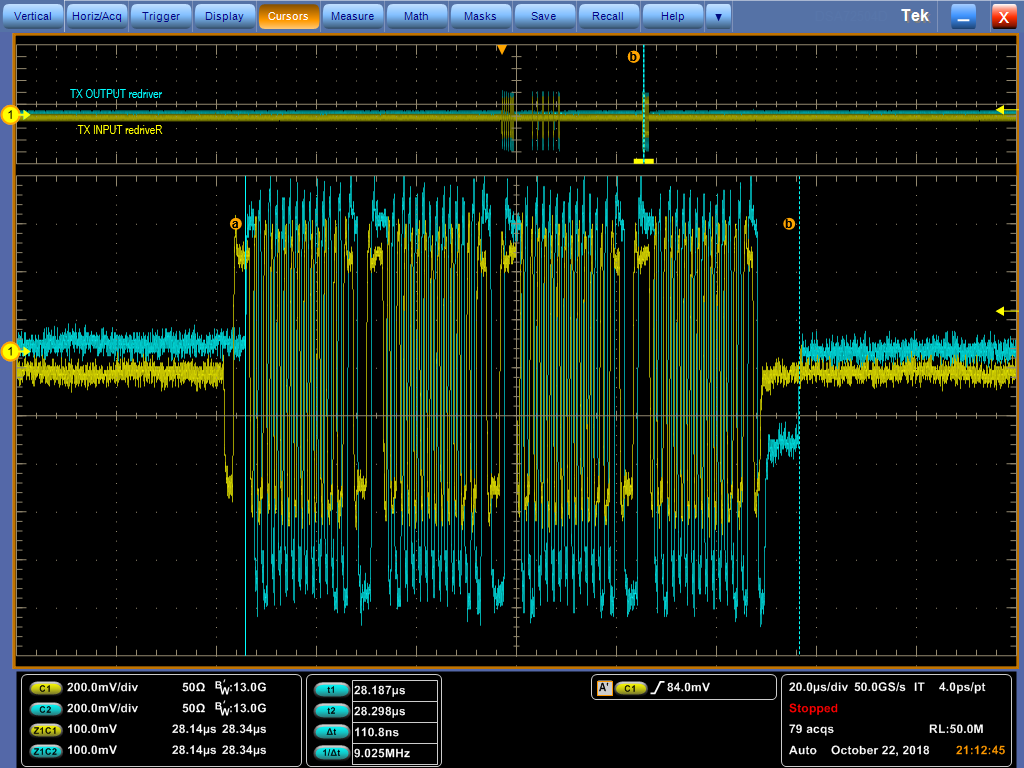

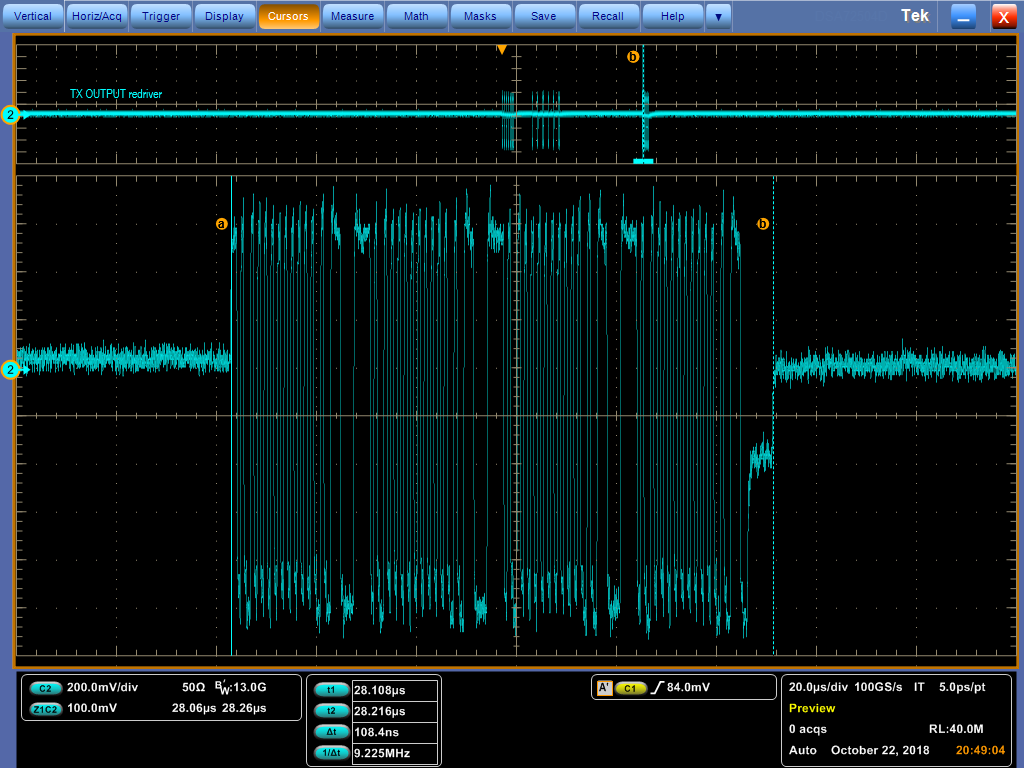

Please refer to below figure.

(Yellow Line is input signal, Blue Line is output signal)

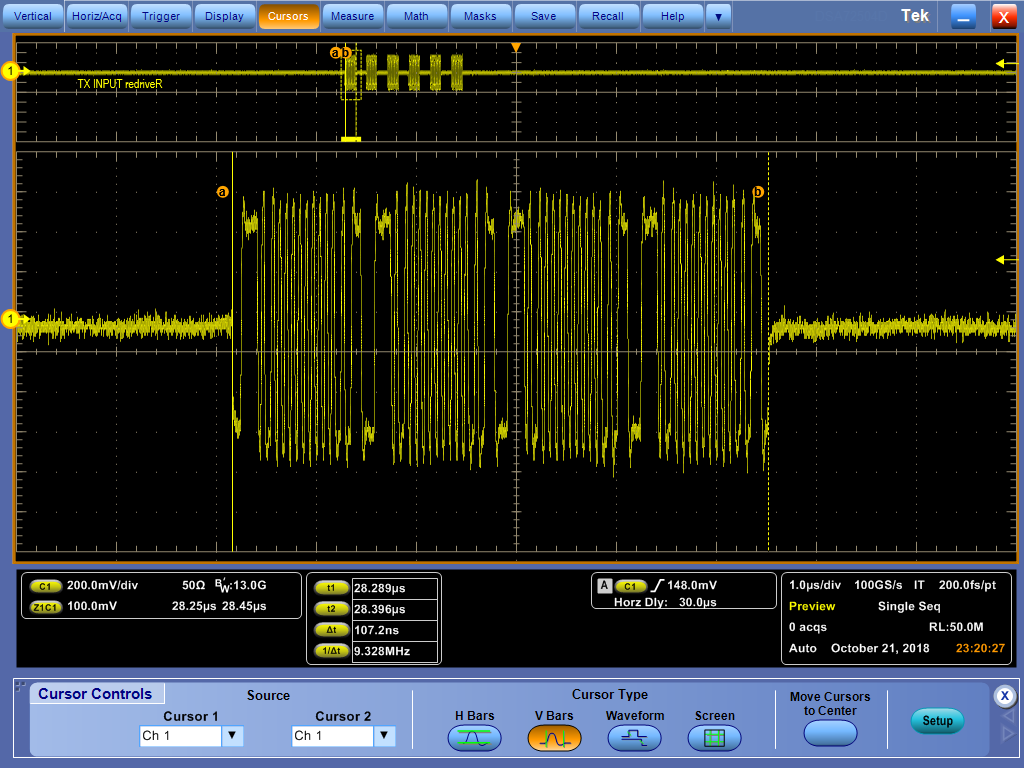

Input OOB signal

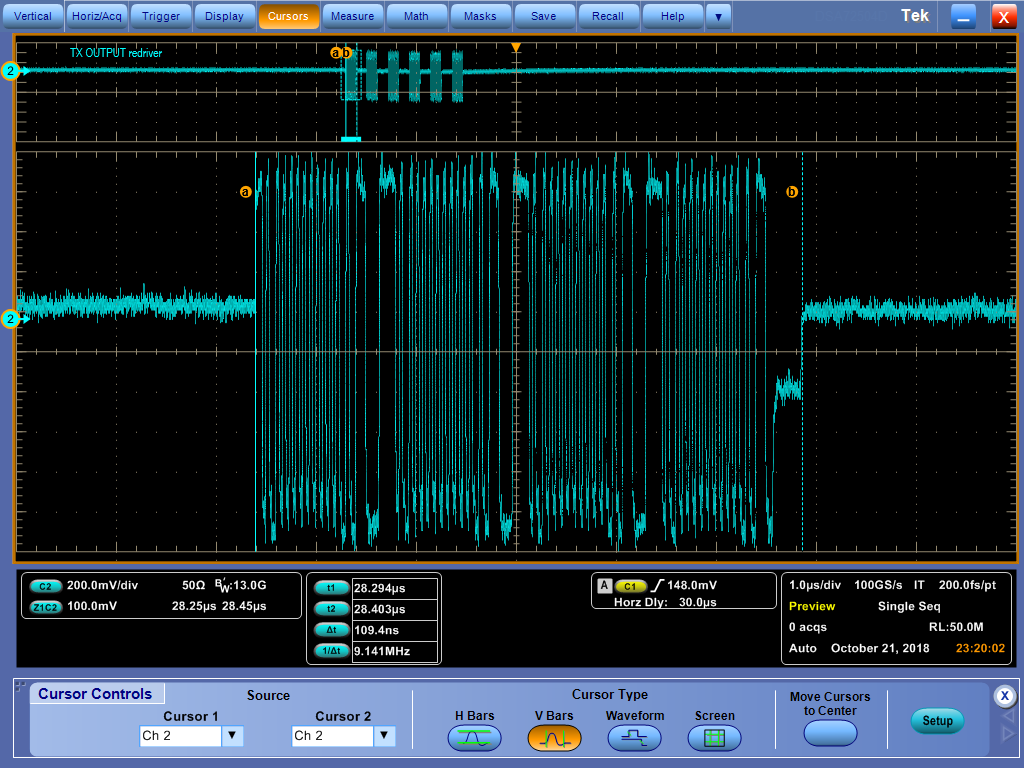

Output OOB signal

Thank you.