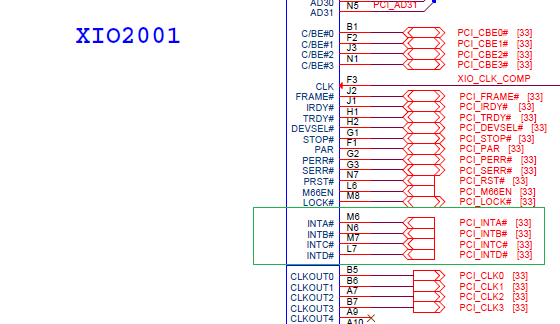

Part Number: XIO2001

Hi Sirs,

Sorry to bother you .

Our customer feedback XIO2001 connect their PCI device then happen spurious interrupts over 10000 times.

We also check the INTA# signal and find over 10000 times low pulse. Their PCI device IC as below.

Have any register setting about this issue? or did you have any experience on this?