Tool/software: Linux

Hello,

We currently have an automotive imaging system that we wish the Enable with Nvidia's Jetson TX2 module.

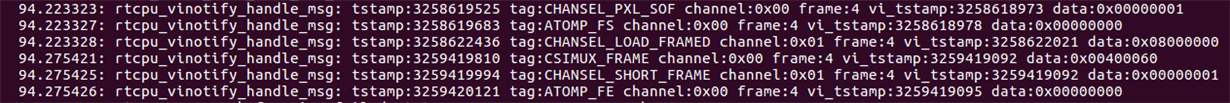

Unfortunately we are having issues in tuning the TX2's MIPI receiver.

From querying the LINE_LENGTH and LINE_COUNT registers, it looks like the MIPI packet consists of

LINE_LENGTH: 2016

LINE_COUNT: 968

I have configured the TX2's CSI receiver to accept these as the input, however I am met with a frame length error.

I am NOT forwarding the truncated 1st line of the frame, however if I DO forward it, the error changes to a "Start of Frame" error

Admittedly I have only written V4L2 drivers for Sensor-only modules, and the LINE_LENGTH is just the # of PIX_CLK periods per line - roughly close to the horizontal resolution of the sensor.

Where does this LINE_LENGTH come from? I.E how is RAW12 1344x968 image generating a line length of 2016?

Is this denoting the number of bytes per line? (1344 x 12/8 = 2016)

Also, would it be worth investigating the FV_MIN_TIME- I currently have it set to 0x04 as I was experiencing issues with this on another system.

Thanks!

-Ryan

System description:

SERDES: DS90UB954 + DS90UB913 (954 is being used to convert the Parallel sensor data to MIPI via the RAW12 HF serialization setting)

ISP: AP102

Sensor: AR0143.

Image Specifications: RAW 12-bit at 1344x968

SERDES Configuration:(sorry for the eyesore, batch wasn't a formatting option lol)

0x7A = DS90UB954 slave address 0xB0 = DS90UB913 "alias" slave address REM Verify communication with deserializer regread 0x7A 8 0x00 8 REM Setup RX Port 0 Fowarding to CSI-0 regwrite 0x7A 8 0x20 8 0xE0 REM Enable CSI-0 in continuous clock mode regwrite 0x7A 8 0x33 8 0x03 REM Enabled RX0 to enable write access to certain registers regwrite 0x7A 8 0x4C 8 0x01 REM Enable RAW12 High-Speed Link for 913 Serializer & Foward all errors, DO NOT forward truncated 1st line

regwrite 0x7A 8 0x6D 8 0x7E

REM Set Minimum Frame Time so Image isnt Skewed regwrite 0x7A 8 0xBC 8 0x04 REM Enable I2C pass through for 933 Serializer regwrite 0x7A 8 0x58 8 0x98 REM Set I2C alias for serializer regwrite 0x7A 8 0x5C 8 0xB0 REM Set I2C slave ID1 to ISP 0x90 address regwrite 0x7A 8 0x5E 8 0x90 REM Set I2C slave ID1 alias to ISP 0x90 address regwrite 0x7A 8 0x66 8 0x90 REM Set I2C slave ID2 to sensor 0x20 address regwrite 0x7A 8 0x5F 8 0x20 REM Set I2C slave ID2 sensor to ISP 0x20 address regwrite 0x7A 8 0x67 8 0x20 REM Pass through and disable pull down resistors on both GPIO0 (D_RESET_N) and GPIO1 (D_F_SYNC) regwrite 0x7A 8 0x6E 8 0x10 regwrite 0x7A 8 0xBE 8 0x03 REM Possible delay here if needed REM DELAY= 2000 REM Verify communication with serializer regread 0xB0 8 0x00 8