Good day,

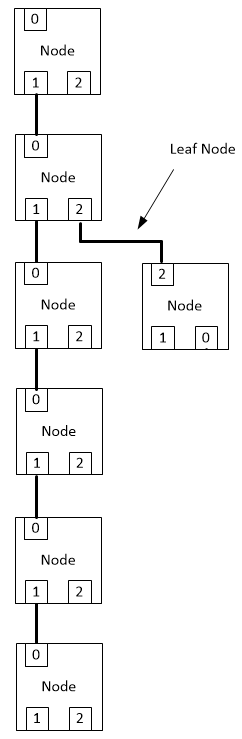

We experience random bus resets, the moment you connect a "leave" node to a network of 30 nodes configured for 1394b ports. A "leave" node is explained below:

The moment you configure the link connected to the leave node to be a 1394A port, the resets disappear. Reading the ERRATA LLZ015C the BOSS arbitration was also solved with this resolution. This make us think this problem are also related to the BOSS arbitration.

Do you have any evidence that this problem was solved with TSB81BA3E silicon or might it still be present? Any suggestion or work around you can suggest?

Regards,

Johan