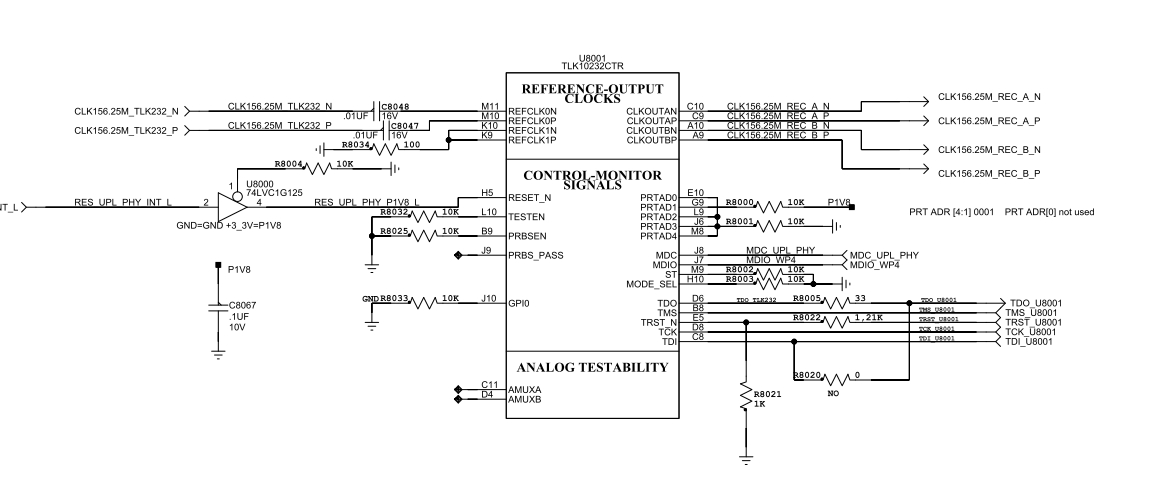

I use 1gbit/s sfp module and configure it to send traffic but could not receive output clock (156.25 MHz) from channel A

device_addr 0x1e, addr 0xf

0x1403

device_addr 0x1e, addr 0x10

0x0

device_addr 0x1e, addr 0xd

0x2f80 possible problem with divider , i tried to set 8 16

device_addr 0x1e, addr 0x2

0x831c

Could you help me how to test it ?