Hello.

I'm trying RGMII mode 100Mbps with the PHY and our MAC.

In case of RGMII mode, I could not see the transmission succeeded whereas the reception was successful.

In my test, the data signals are output from the MAC to the PHY. And then, the PHY output coded signals to my PC. And the PC captures it.

Because I could confirm the transmission in MII 100Mbps mode, HW from the PHY to my PC should be OK.

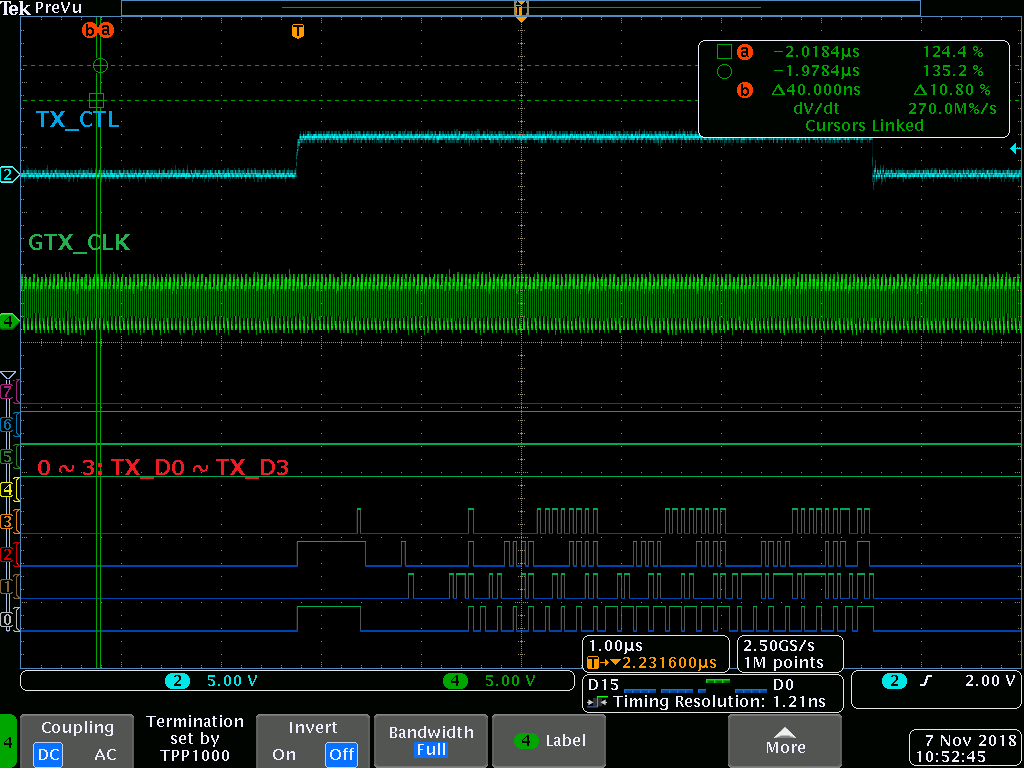

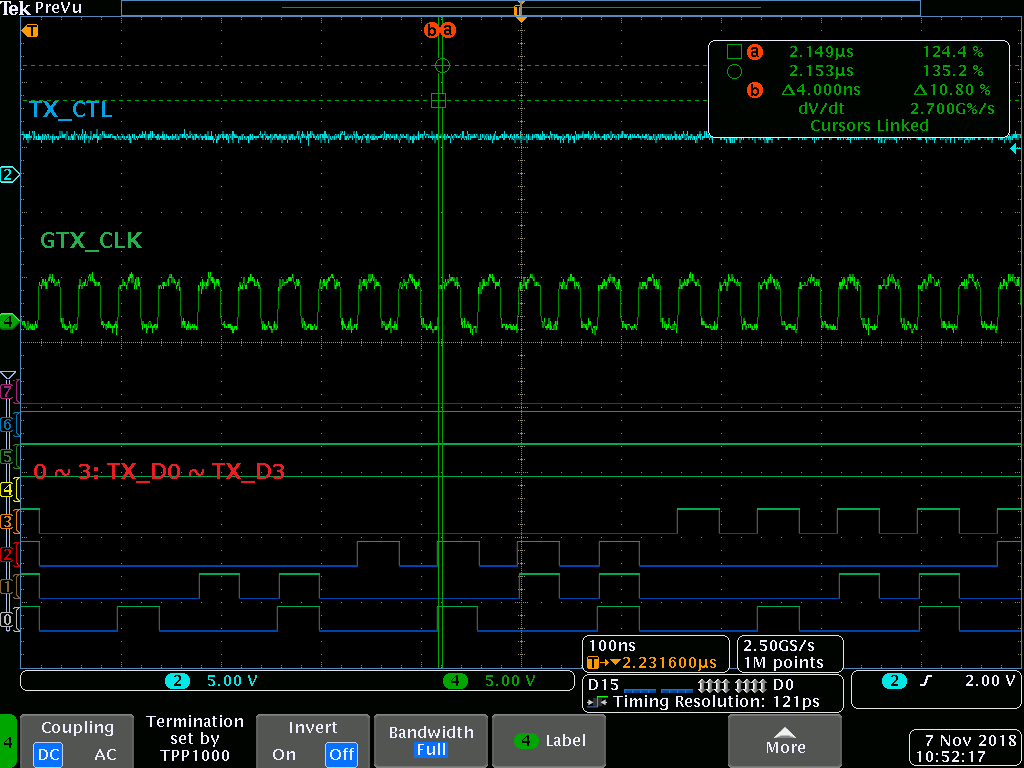

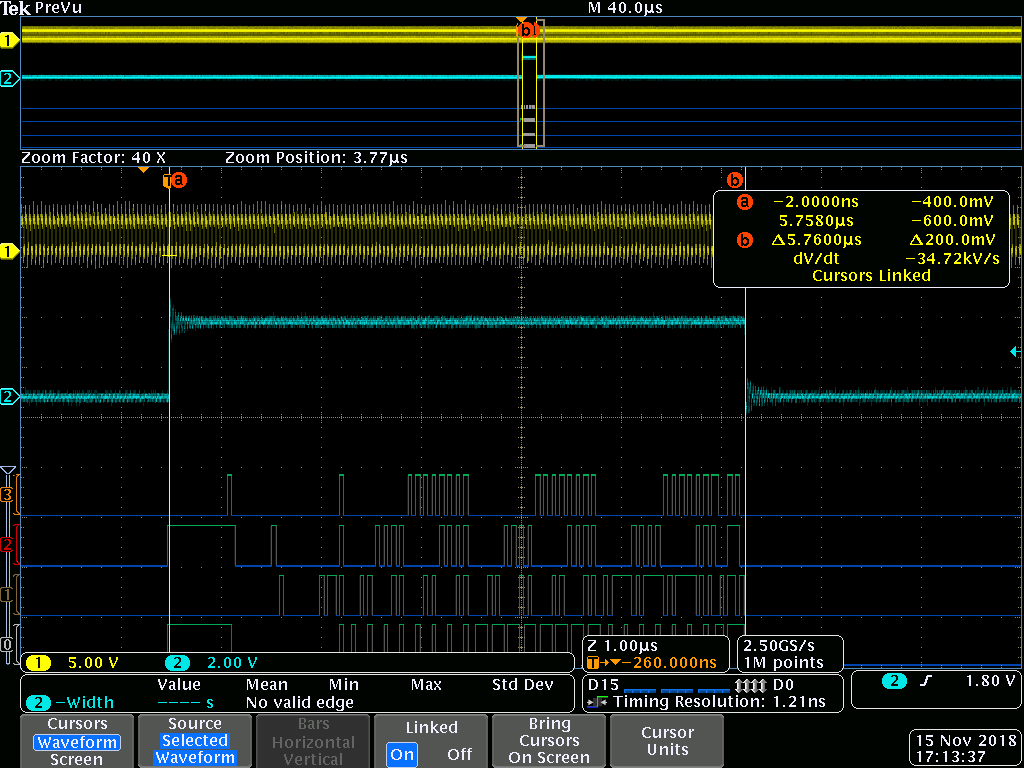

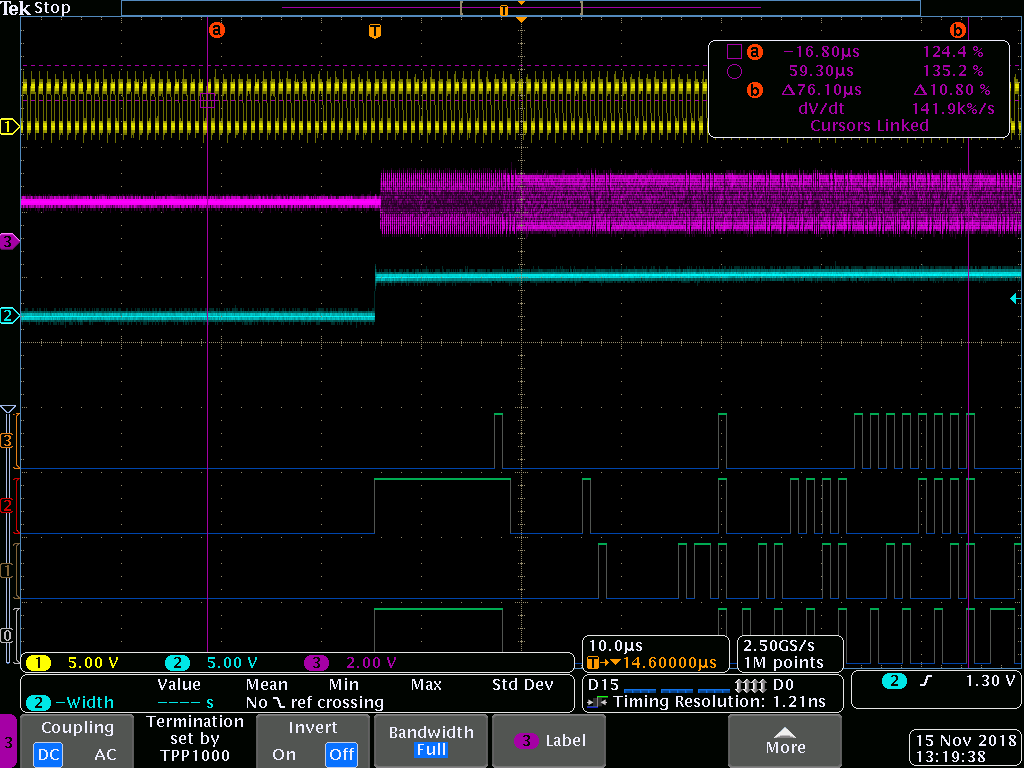

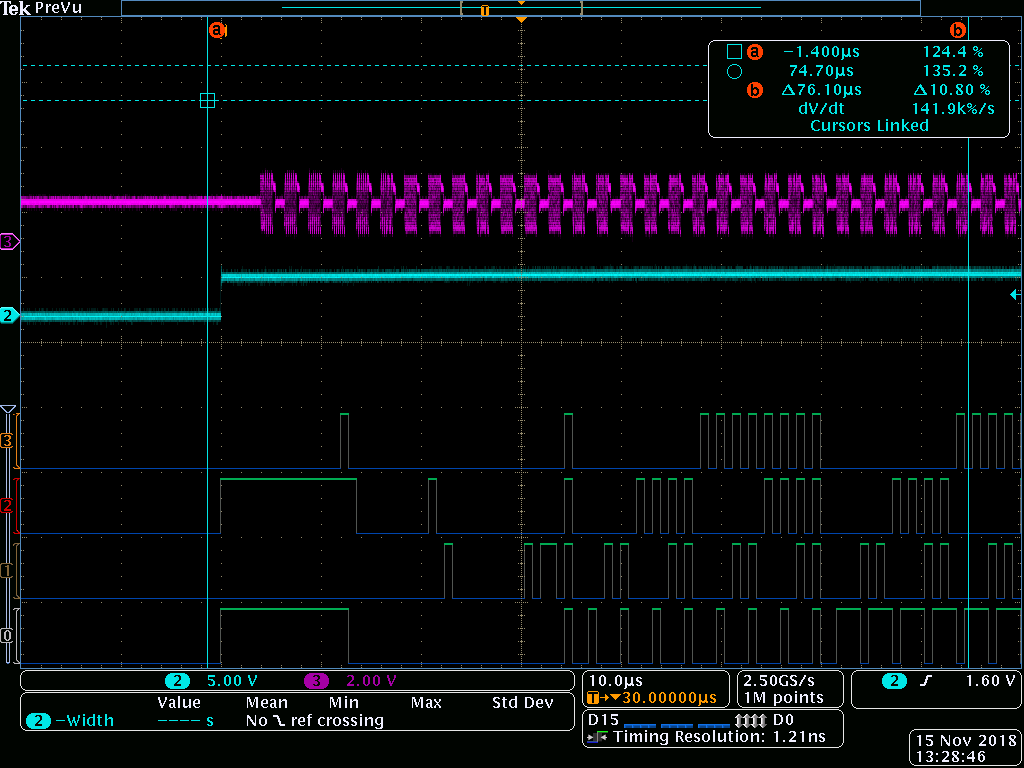

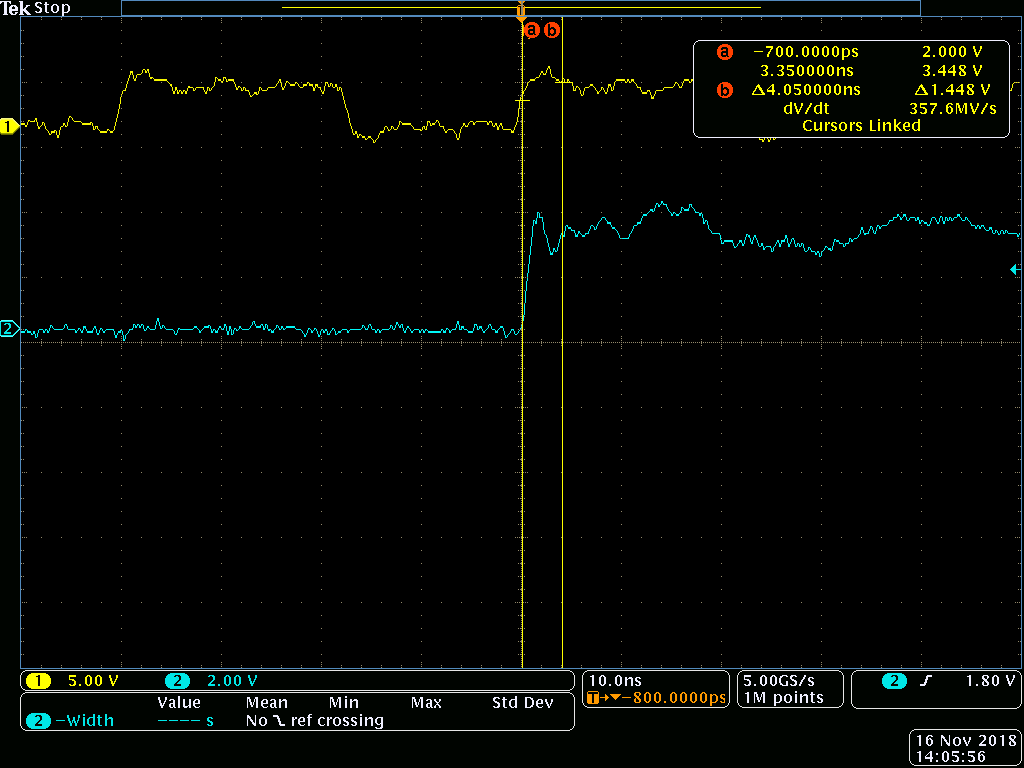

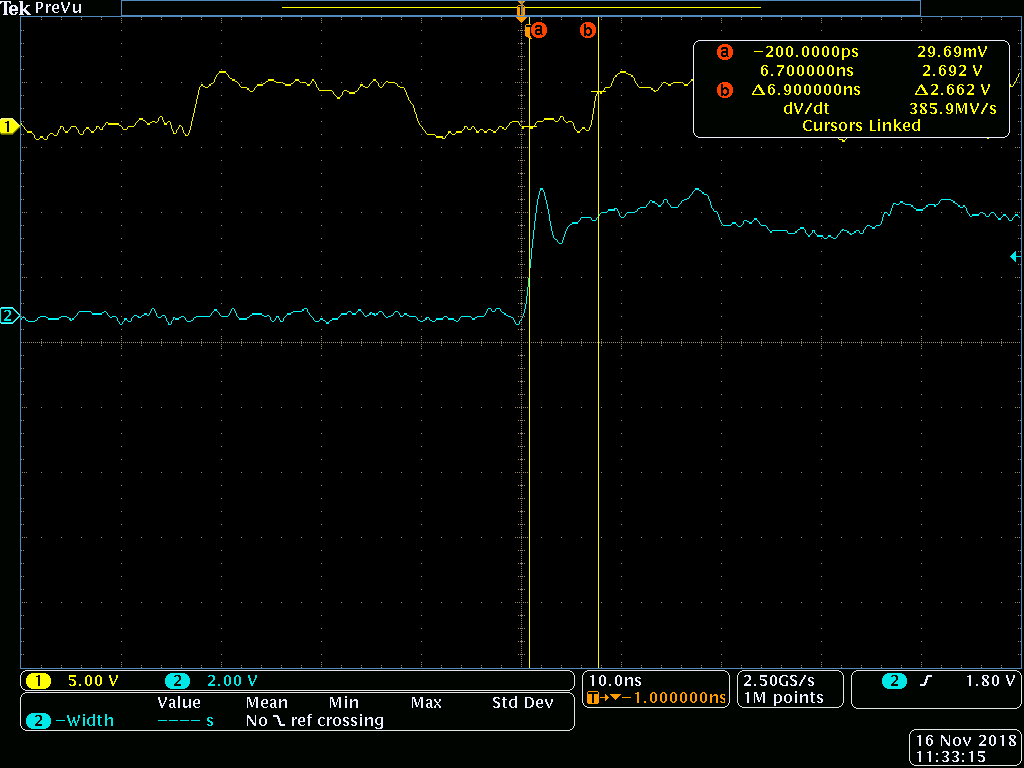

I attached image files of the signals from the MAC by an oscilloscope at the bottom. If internal delay added, it looks no problem.

A clock for transmission data is output from the MAC and goes to "GTX_CLK" (not TX_CLK) of the PHY.

Register settings for the PHY are shown in below. I confirmed these register were set as expected with reading back the values.

Address : Value

0x0000: 0x2100 /** 100M, Full Duplex and Auto Negotiation OFF */

0x0010: 0x5028 /** Disable auto neg for MDI/MDI-X **/

0x0032: 0x00D3 /** Enter Tx and RX Clock delay in RGMII configuration register */

0x0086: 0x00FF /** Internal Delay Configuration : 4ns */

I appreciate it if you give me any suggestion.

Is there any lack in my settings?

Best regards,

Tsunokawa