Dear E2E Support,

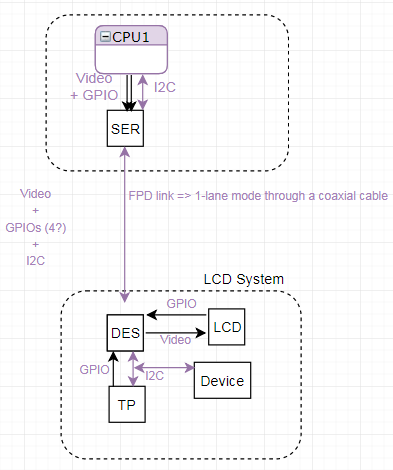

My customer intend to use our DS90UB948/9 Ser-Des solutions, as shown in the bloc diagram below:

- could you confirm that it's possible to connect multiple devices on the I2C bus (behind the Deserializer)?

- what is the effective I2C bandwidth regarding the whole serial interface?

- could you confirm that the following configuration is supported with a 1-lane interface using a coaxial cable, knowing that it should support video of 1280x800, with a pclk=71.1MHz (60fps)?

Regards,