Other Parts Discussed in Thread: ALP, DP83640T-EVK, DP83640

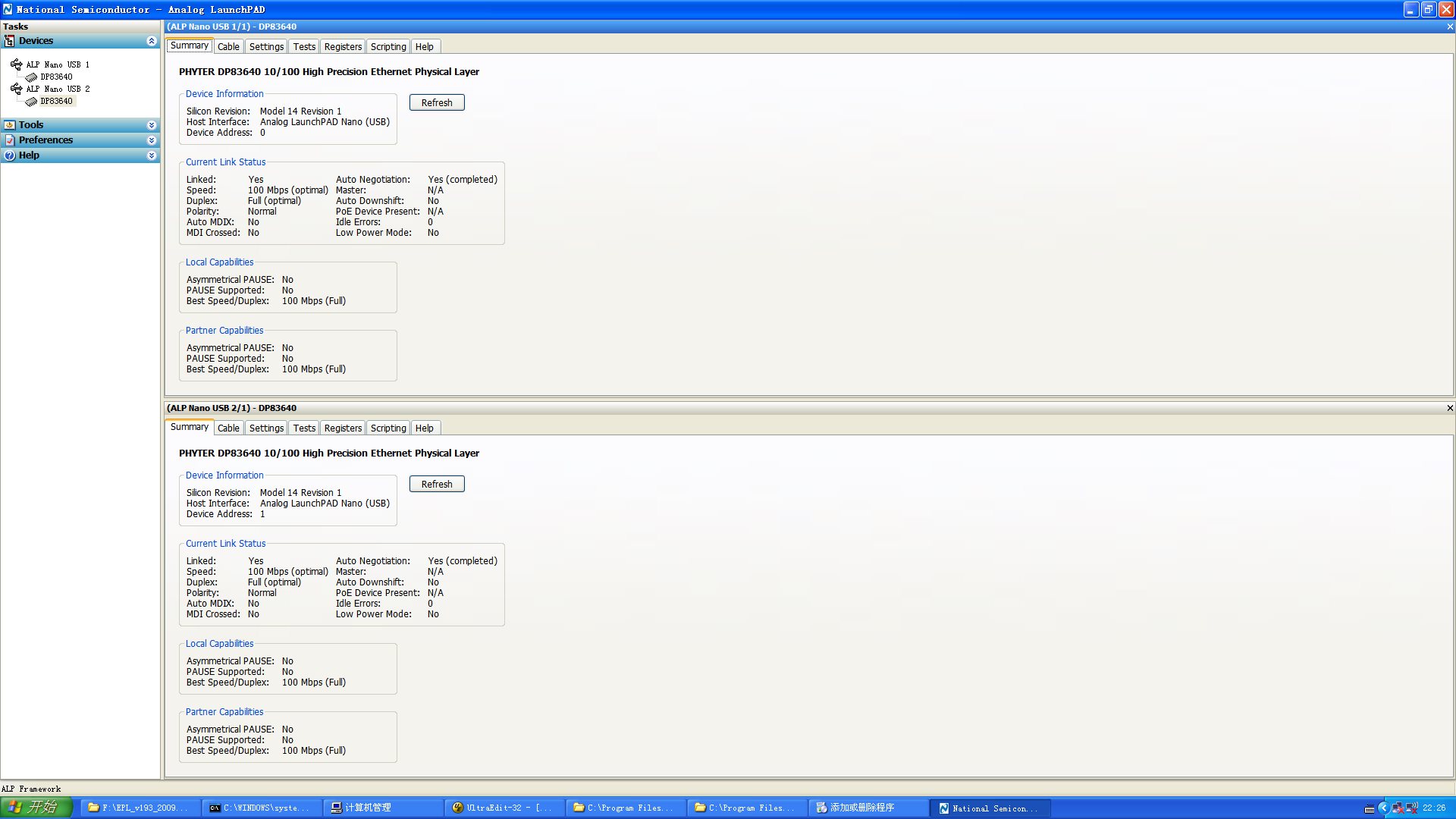

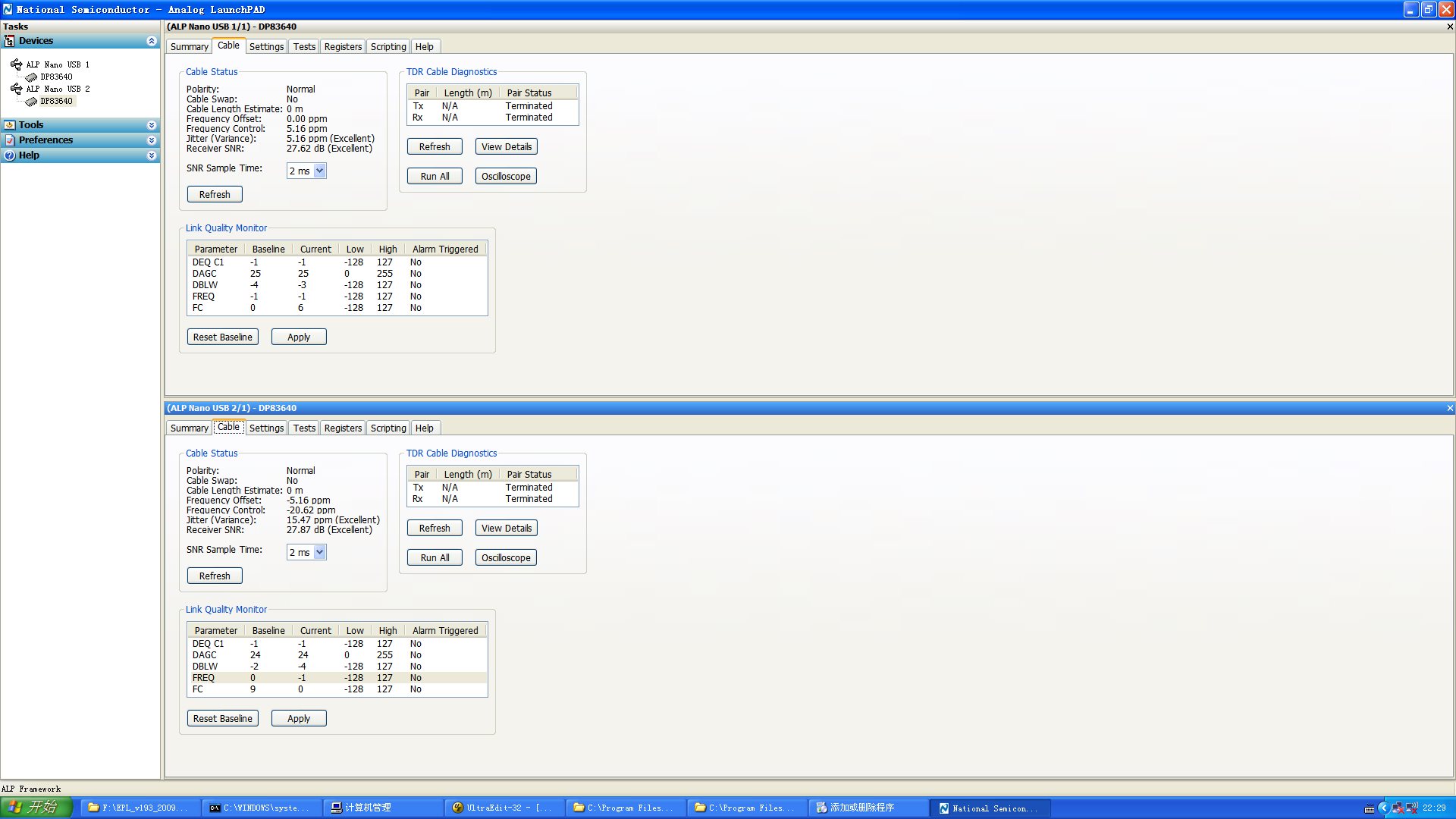

I have two DP83630-EVK(s), connect them with CAT5 cable (1meter long).

Then LED SPEED and LINK lights up, it seems like them connect successful.

I use a PC with Windows XP , then installed drivers and ALP software.

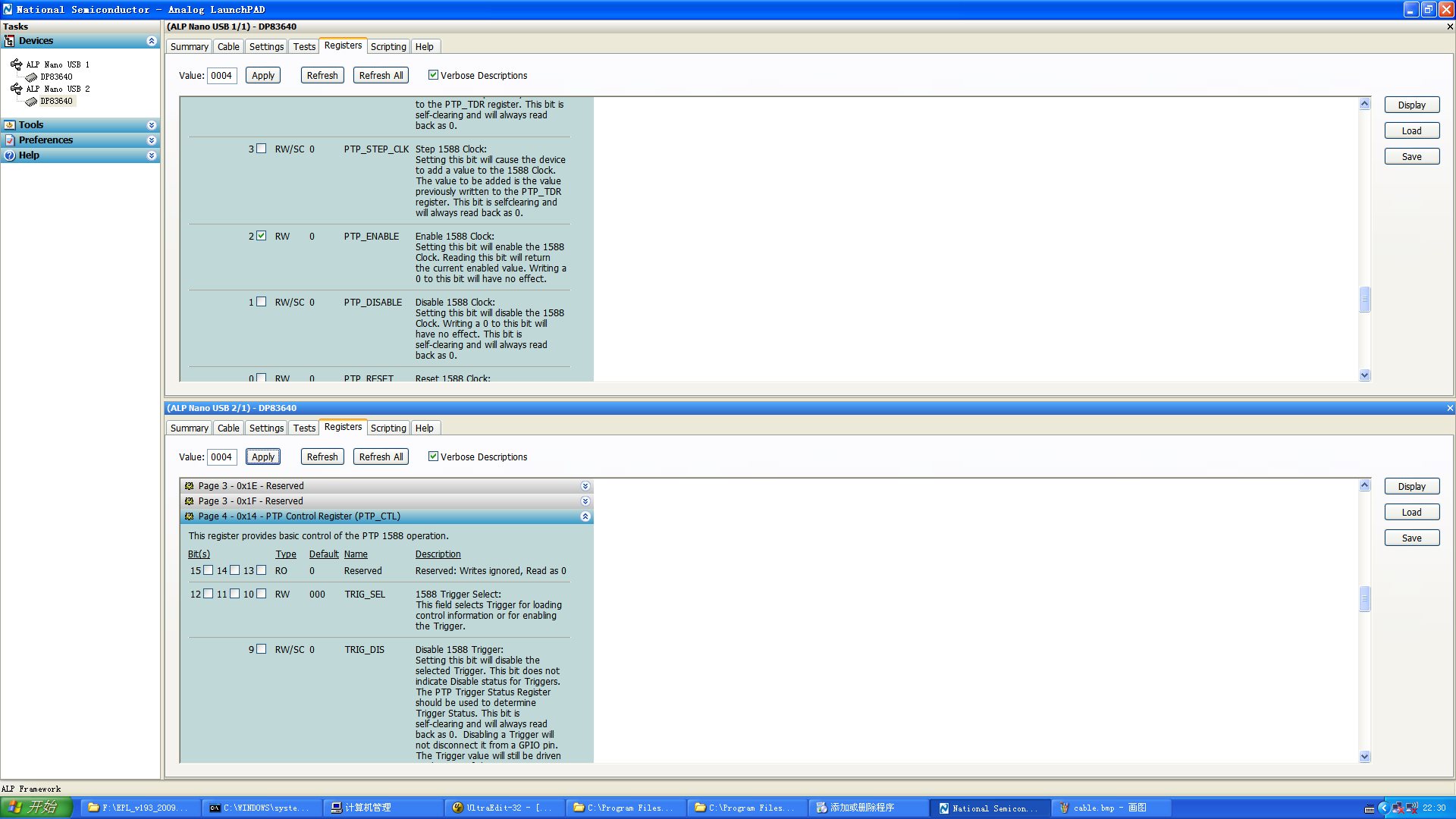

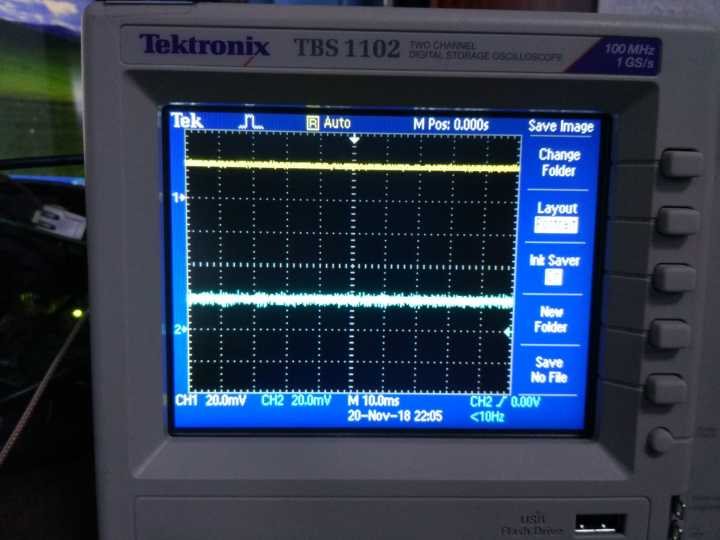

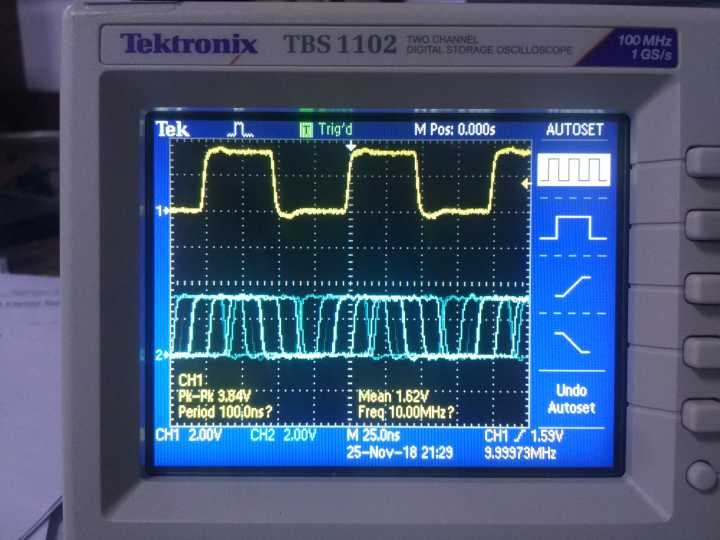

By using ALP write reg 0x14 as 0x0004, CLK_1588/CLK_OUT still stuck at GND.

Connect Pic:

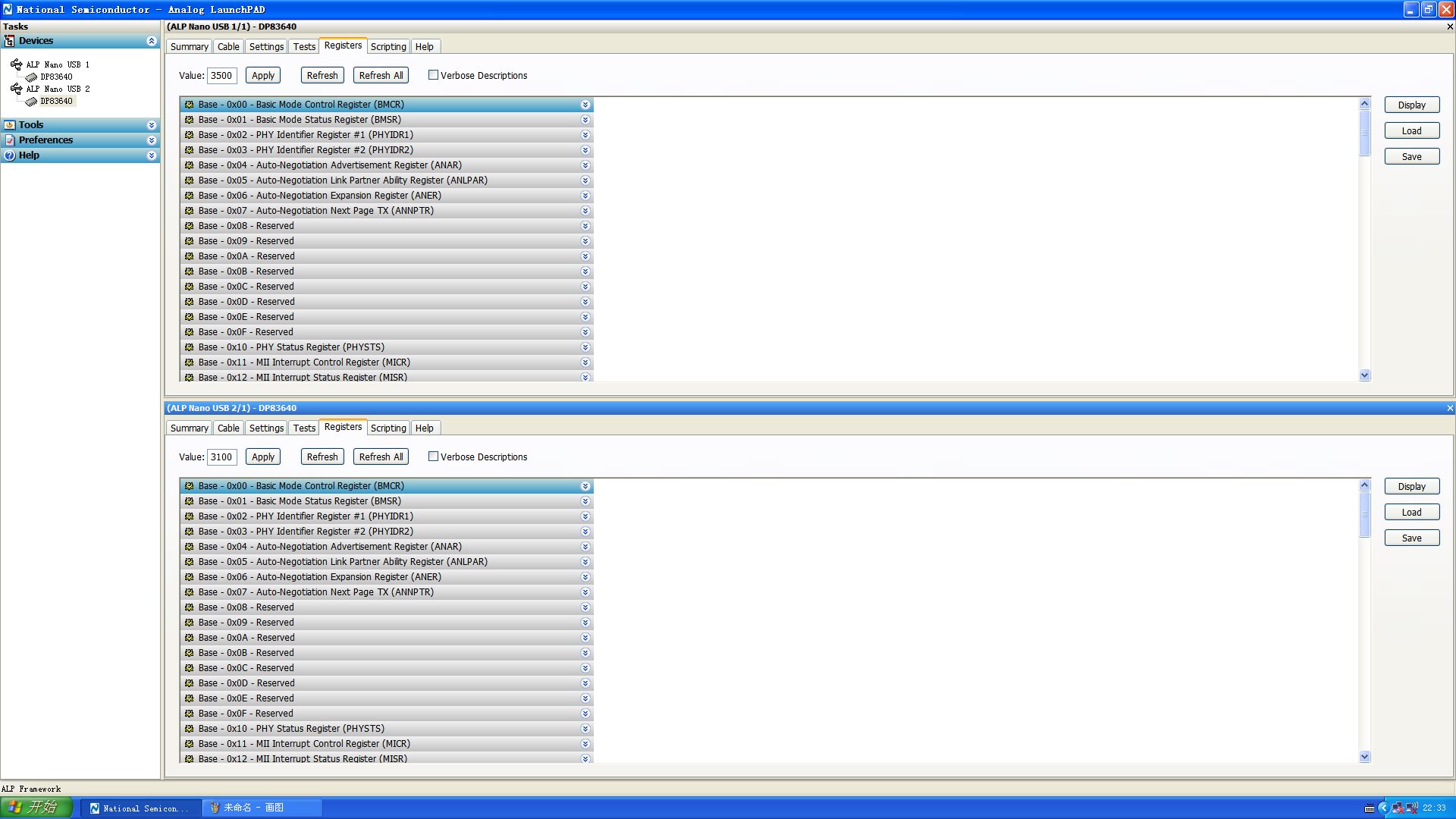

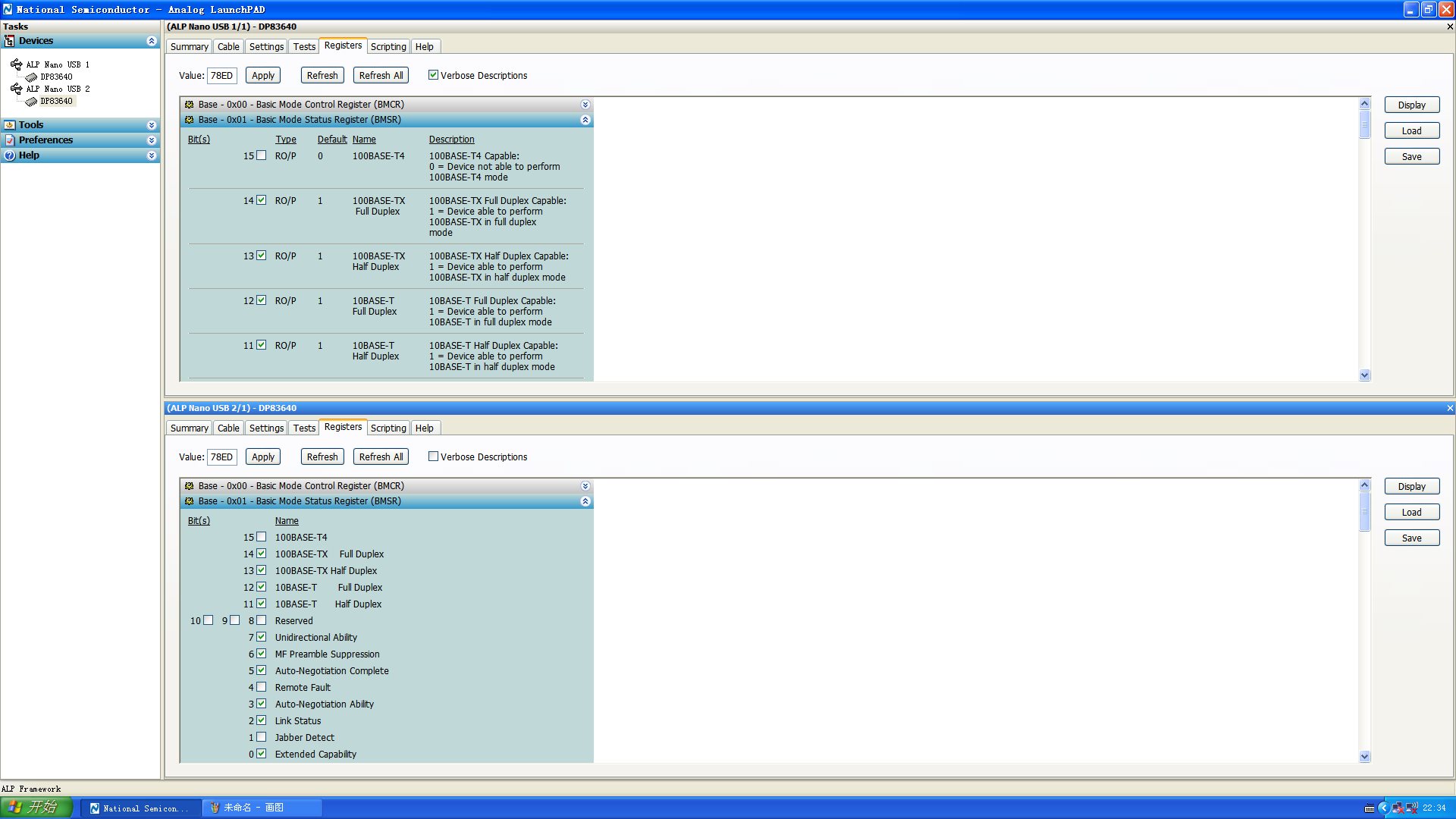

ALP settings :

Write Reg 0x14 as 0x0004

Output: