Other Parts Discussed in Thread: ALP, DP83640

I have two DP83640-EVK and connect with CAT-5 cable.

I need get same phase CLK in two DP83640-EVK. So I try to align CLK_OUT From PTP.

I try to use ALP to do Phase Alignment (from AN-1729 3.2 Phase Alignment)

I do following things in ALP:

1. Write 0x0000 to PHYCR2 (Page 0 Reg 0x1C) in Master DP83640 to enable CLK_OUT

2. Write 0x2000 to PHYCR2 (Page 0 Reg 0x1C) in Slave DP83640 to enable CLK_OUT and Enable Synchronous Ethernet.

3. Write 0x8019 to PTP_COC (Page 6 Reg 0x14) in both DP83640 , set CLK_OUT as 10MHz.

4. Write 0x0004 to PTP_CTL (Page 4 Reg 0x14) in both DP83640 , Enable PTP 1588.

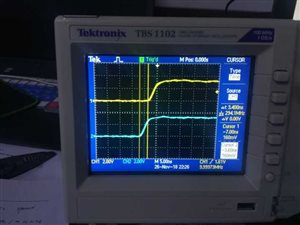

And now the CLK_OUT between two DP83640 phase error is ~3.4ns. (Sometimes it will more than 40ns , 3.4ns is the best one)

Figure 1 Phase error

5. Write 0x1CE1 and then Write 0x5CE1 to PTP_EVNT (Page 5 Reg 0x15) in Slave DP83640

ALP shows me it self cleared, read back is 0x1C01 And 5C01.

6. Read PTP_ESTS (Page 4 Reg 0x1E),it is 0x00E1 , correct.

7. Read PTP_EDATA (Page 4 Reg 0x1F) four times, they are : 0xAD28,0x1BCA,0x0051,0x0000

So I get PTP timestamp 0x0000_0051_1BCA_AD28 -> it mod 100 is 78. (or -22)

8. And then Do same things to Master DP83640.

Get 0x0000_06FD_07C8_2488 it mod 100 is 08.

9. Write PTP_TDR 78+16 = 0x005E to PTP_TDR

and Write 0x000C to PTP_CTL

Nothing happed... Two CLK_OUT still have phase error.

How can I adjust CLK_OUT phase?

My application need aligned phase clock feed.

Or I need use external devices to adjust phase? (Such as Altera/Intel FPGA built-in PLL)

I found some same thread in e2e, but no answers: