Other Parts Discussed in Thread: TINA-TI

Tool/software: TINA-TI or Spice Models

Hi Team,

My customer is seeing the following when using the x934 de-serializer IBIS model.

Issue observed:

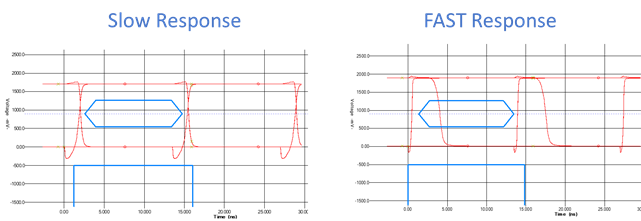

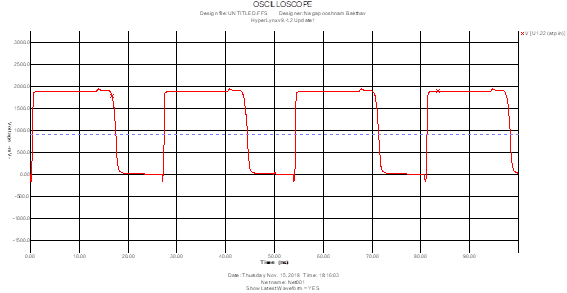

Deserializer ROUT lines response during Fast corner and Typical corner are having an issue of having duty cycle more than 50%, whereas the provided input duty cycle is 50%.

FYR, Fast Response with Stimulus provided: Oscillator of 37.125MHz