Other Parts Discussed in Thread: SN65DSI83, DSI-TUNER

Hello,

We are using SN65DSI83 bridge chip with our application processor to convert 4 lane MIPI DSI data to 4 lane LVDS data. Below is our configuration.

DSI:

4 data lane + 1 clock lane

DSI clock - 683 MHz 342 MHz

LVDS:

Pixel clock - 113 MHz

Refresh rate - 50Hz

Resolution (WxH) - 1920*1080

H-front-porch- 10

H-back-porch - 70

H-sync-pulse-width - 10

V-front-porch - 10

V-back-porch - 30

V-sync-pulse-width - 10

Bits/Pixel - 24bit/RGB

Ref clock - DSI continuous clock

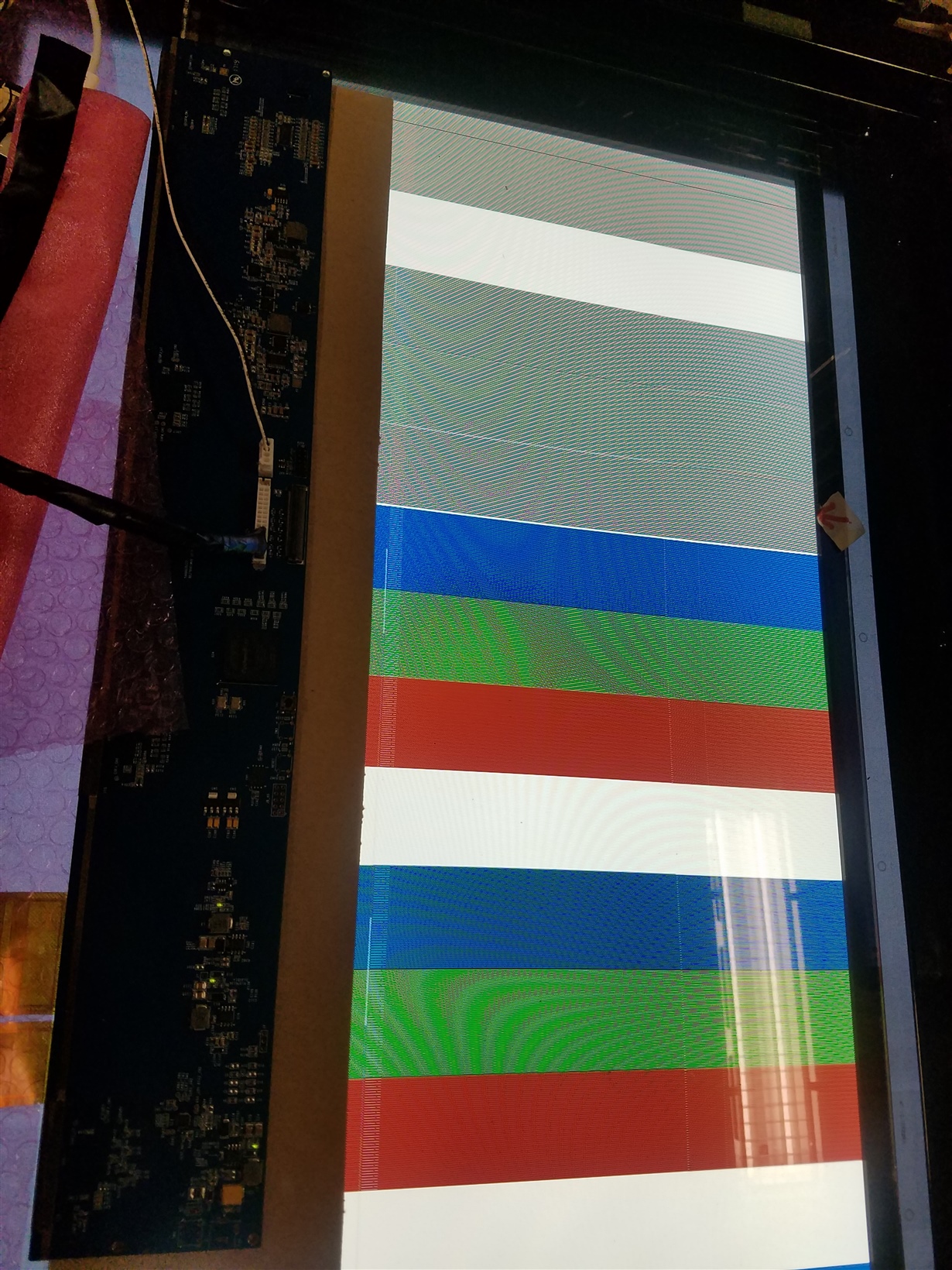

We have tried generated test pattern but it's distorted and flickering. Also, a portion of the test pattern is greyed out and overlapped.

Queries/Observations:

1. SN65DSI83 will be able to support this resolution? As per SN65DSI83 datasheet, it can support up to 1920x1080@60fps.

2. What should be configured for the correct test pattern?

3. After applying the attached test pattern configuration - register 0xE5 is set to 0xC1, indicating sync/CRC error? What's the root cause for this?

4. We are able to get the data from DSI and display it on the LVDS, but same way - it's overlapped and a portion of the display is greyed out.

Please provide your input.

Thanks.