Part Number: TMDS181

hi dear supporting team,

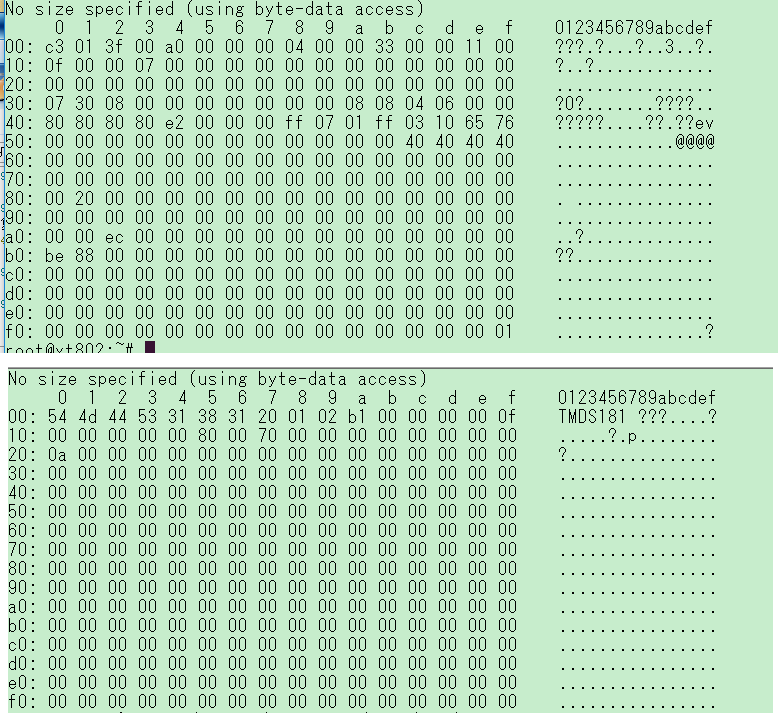

customer is using TMDS181 for HDMI input, the video source is 4kP30 HDMI signal, the data rate is 3.94G, clk rate is 297M. they found when the cable length is shorter than 1.5m, it is ok. while when it is 2.8m, then the FPGA IP core follow the TMDS181 will not recognize the video source. and if change TMDS181 mode to redrive mode will be better than retimer mode.

they also test FPGA evk without 181 on it with the same cable lengther, the EQ used is from FPGA. the result is very stable.

so what's the possible problem? ( is the additive jitter of 181 cause the issue? ) thanks a lot!