Other Parts Discussed in Thread: AM3358

Good day,

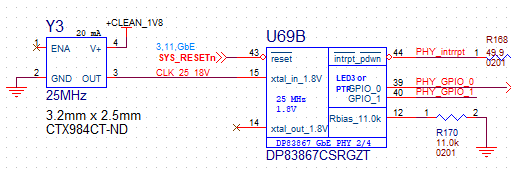

In one of the hardware designs I have been working with, the DA1T002I3 (link) stacked RJ45 connector with magnetics is being used. In the process of the design evolution earlier this year, the DP83867CS has been put in place of an older Marvel chip (that originally called for the magnetics configuration of the DA1T002I3).

The combo of AM3358 + DP83867CS + DA1T002I3 seems has been working pretty good, with the following two observations which we are trying explain:

1) The iperf measurements consistently show 308 Mbps TX and 421 Mbps RX, but the earlier design AM3358 + Marvell+ DA1T002I3 obtained 365 Mbps TX and 428 Mbps RX.

2) When the design with DP83867CS is connected to a Netgear GS750E switch the TX rate is as above, but the RX rate drops to 370 Mbps and ethtool reports some RX CRC Errors (less than a dozen per 1 GB received), Align/Code Errors (~20 per 1GB received), RX Jabbers (~50-100 per 1 GB received). Probing with the scope I can see that the RX_CTRL toggles unexpectedly.

When a GS108 switch is placed in-line between the DP83867CS and GS750E (or just GS108 is used) the RX rate goes back up to 421 Mbps and no errors/jabbers are reported by ethtool. Also, RX_CTRL does not toggle unexpectedly.

And today I just came upon this thread from last month: "DP83867E: RJ-45 Connector supported by DP83867ergz Phy" which points out that the using magnetics with individual transformer middle taps is critical to DP83867 PHYs.

Since the magnetics in the DA1T002I3 have all the transformer middles tied together:

1) Can this in the long term damage the DP83867CS or is it impacting only signal integrity?

2) Can this explain the reduced performance and sensitivity to the network switches?

If a connector change is absolutely needed, connectors such as this one 0845-2R1T-E4 should work?

Thank you for your time and help.