Other Parts Discussed in Thread: DS90UB913Q-Q1, DS90UB913A-Q1

Hi,I have a problem with DS90UB954,DS90UB913.The size of image is wrong.

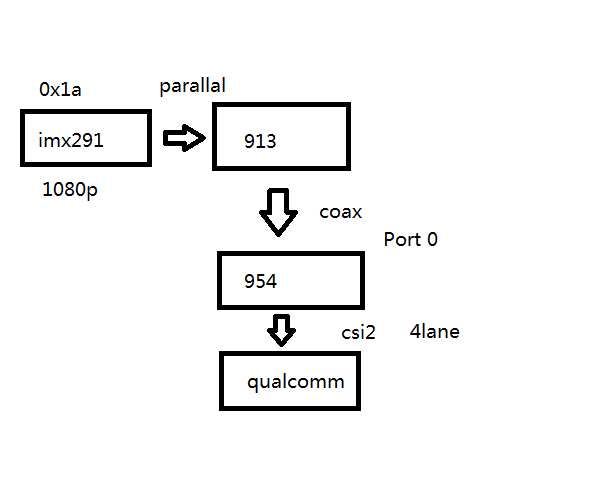

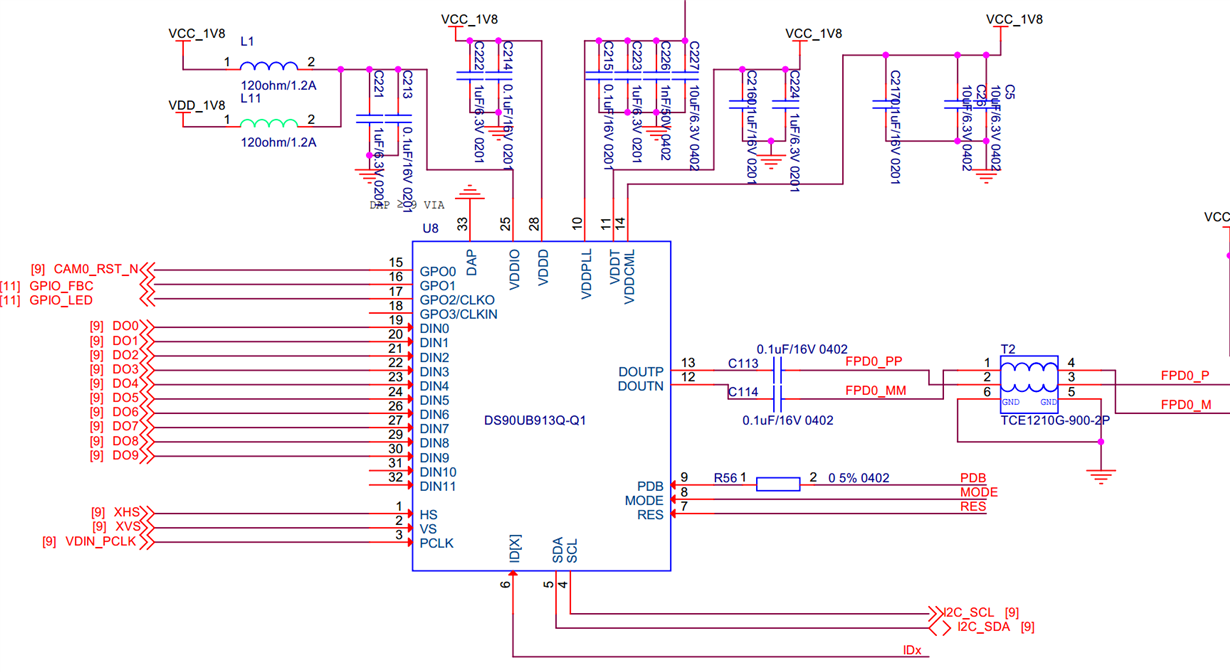

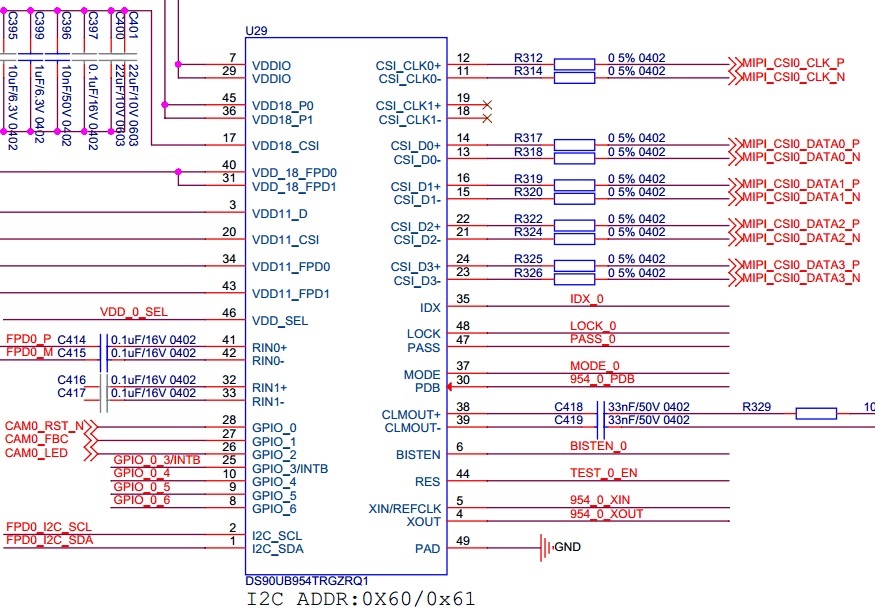

Our circuit as follows:

IMX291 ---> DS90UB913 ---> DS90UB954 ---> Qualcomm CPU

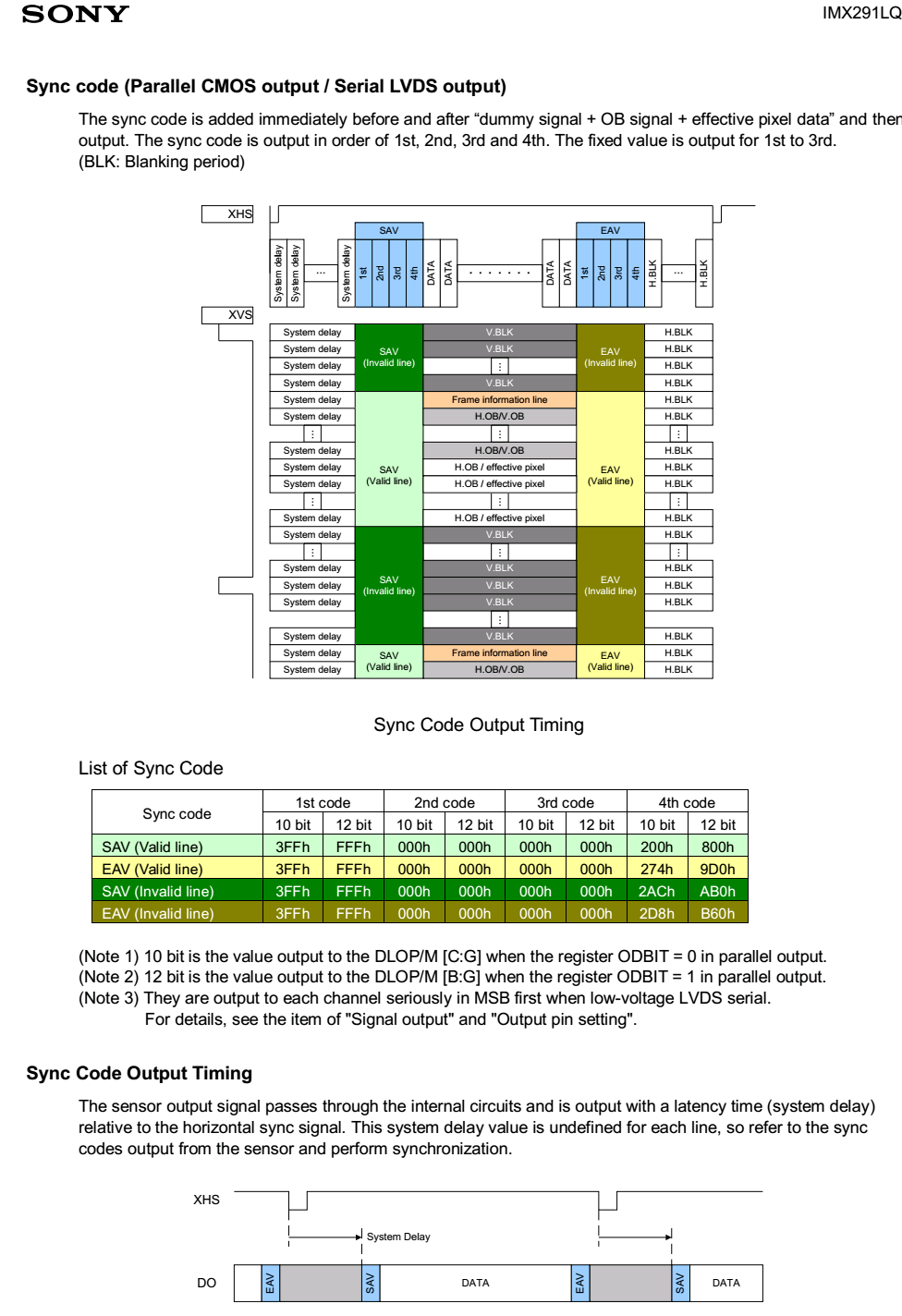

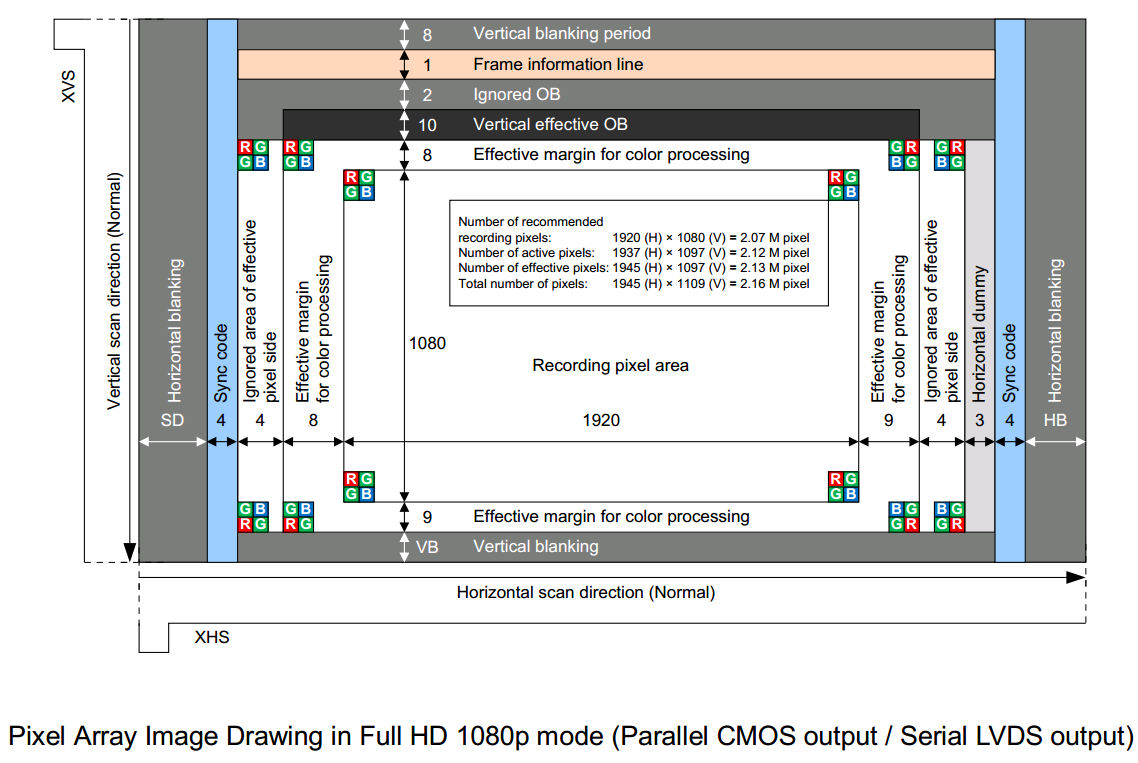

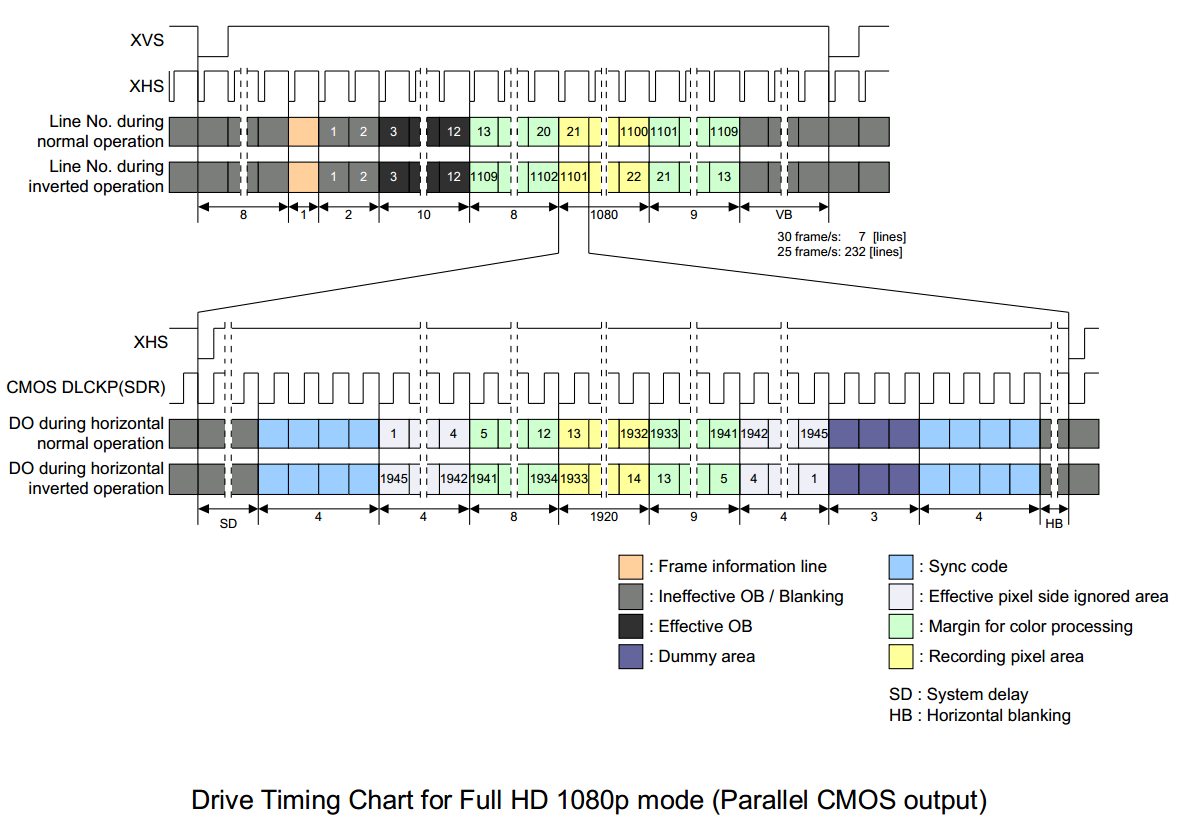

IMX291:Parallel CMOS output, 10bit, 1945x1097, Full HD 1080p, 30fps, 74.25Mpixel/s

DS90UB913 Registers Dump:

Reg[0x00]:0xb0 Reg[0x01]:0x30 Reg[0x02]:0x20 Reg[0x03]:0xc7 Reg[0x04]:0x80 Reg[0x05]:0x14 Reg[0x06]:0xd1 Reg[0x07]:0x00 Reg[0x08]:0xd0

Reg[0x09]:0xd0 Reg[0x0a]:0x02 Reg[0x0b]:0x00 Reg[0x0c]:0x17 Reg[0x0d]:0x55 Reg[0x0e]:0x35 Reg[0x0f]:0x18 Reg[0x10]:0x17

Reg[0x11]:0x65 Reg[0x12]:0x65 Reg[0x13]:0x00 Reg[0x14]:0x00 Reg[0x1e]:0xfe Reg[0x2a]:0x00 Reg[0x2d]:0x00 Reg[0x35]:0x00

DS90UB954's regs as follows:

DS90UB954 Registers Dump:

Reg[0x00]:0x60 Reg[0x01]:0x00 Reg[0x02]:0x1e Reg[0x03]:0x20 Reg[0x04]:0xdf Reg[0x05]:0x01 Reg[0x06]:0x00 Reg[0x07]:0xfe Reg[0x08]:0x1e

Reg[0x09]:0x1c Reg[0x0a]:0x78 Reg[0x0b]:0x78 Reg[0x0c]:0x81 Reg[0x0d]:0x09 Reg[0x0e]:0x01 Reg[0x0f]:0x01 Reg[0x10]:0x00

Reg[0x11]:0x13 Reg[0x12]:0x13 Reg[0x13]:0x81 Reg[0x14]:0x13 Reg[0x15]:0x13 Reg[0x16]:0x13 Reg[0x17]:0x00 Reg[0x18]:0x00

Reg[0x19]:0x00 Reg[0x1a]:0x00 Reg[0x1b]:0x00 Reg[0x1c]:0x00 Reg[0x1d]:0x00 Reg[0x1e]:0x04 Reg[0x1f]:0x03 Reg[0x20]:0x20

Reg[0x21]:0x01 Reg[0x22]:0x00 Reg[0x23]:0x00 Reg[0x24]:0x00 Reg[0x25]:0x00 Reg[0x26]:0x00 Reg[0x27]:0x00 Reg[0x28]:0x00

Reg[0x29]:0x00 Reg[0x2a]:0x00 Reg[0x2b]:0x00 Reg[0x2c]:0x00 Reg[0x2d]:0x00 Reg[0x33]:0x01 Reg[0x34]:0x40 Reg[0x35]:0x01

Reg[0x36]:0x00 Reg[0x37]:0x01 Reg[0x39]:0x00 Reg[0x3a]:0x00 Reg[0x41]:0xa7 Reg[0x42]:0x71 Reg[0x43]:0x01 Reg[0x4a]:0x10

Reg[0x4b]:0x12 Reg[0x4c]:0x01 Reg[0x4d]:0x13 Reg[0x4e]:0x45 Reg[0x4f]:0x25 Reg[0x50]:0x20 Reg[0x51]:0x00 Reg[0x52]:0x00

Reg[0x53]:0x00 Reg[0x54]:0x00 Reg[0x55]:0x00 Reg[0x56]:0x00 Reg[0x57]:0x00 Reg[0x58]:0x58 Reg[0x59]:0x00 Reg[0x52]:0x00

Reg[0x53]:0x00 Reg[0x54]:0x00 Reg[0x55]:0x00 Reg[0x56]:0x00 Reg[0x57]:0x00 Reg[0x58]:0x58 Reg[0x59]:0x00 Reg[0x5a]:0x00

Reg[0x5b]:0xb0 Reg[0x5c]:0xb0 Reg[0x5d]:0x34 Reg[0x5e]:0x00 Reg[0x5f]:0x00 Reg[0x60]:0x00 Reg[0x61]:0x00 Reg[0x62]:0x00

Reg[0x63]:0x00 Reg[0x64]:0x00 Reg[0x65]:0x34 Reg[0x66]:0x00 Reg[0x67]:0x00 Reg[0x68]:0x00 Reg[0x69]:0x00 Reg[0x6a]:0x00

Reg[0x6b]:0x00 Reg[0x6c]:0x00 Reg[0x6d]:0x7f Reg[0x6e]:0x80 Reg[0x6f]:0x88 Reg[0x70]:0x2b Reg[0x71]:0x2c Reg[0x72]:0xe4

Reg[0x73]:0x02 Reg[0x74]:0x32 Reg[0x75]:0x0a Reg[0x76]:0xb4 Reg[0x77]:0xc5 Reg[0x78]:0x00 Reg[0x79]:0x01 Reg[0x7a]:0x00

Reg[0x7b]:0x00 Reg[0x7c]:0x20 Reg[0x7d]:0x00 Reg[0x7e]:0x00 Reg[0x7f]:0x00 Reg[0xa5]:0x18 Reg[0xb0]:0x02 Reg[0xb1]:0x49

Reg[0xb2]:0x00 Reg[0xb3]:0x08 Reg[0xb8]:0x8f Reg[0xb9]:0x33 Reg[0xba]:0x83 Reg[0xbc]:0x80 Reg[0xbe]:0x00 Reg[0xd0]:0x00

Reg[0xd2]:0x94 Reg[0xd3]:0x03 Reg[0xd4]:0x60 Reg[0xd5]:0xf2 Reg[0xd8]:0x00 Reg[0xd9]:0x00 Reg[0xda]:0x00 Reg[0xdb]:0x00

Reg[0xdc]:0x00 Reg[0xdd]:0x00 Reg[0xde]:0x00 Reg[0xdf]:0x00 Reg[0xf0]:0x5f Reg[0xf1]:0x55 Reg[0xf2]:0x42 Reg[0xf3]:0x39

Reg[0xf4]:0x35 Reg[0xf5]:0x34 Reg[0xf8]:0x00 Reg[0xf9]:0x00

However the CPU linux kernel log show as follows:

[ 69.514155] ispif_process_irq: PIX0 frame id: 0

[ 69.547509] ispif_process_irq: PIX0 frame id: 1

[ 69.580837] ispif_process_irq: PIX0 frame id: 2

[ 69.580894] msm_isp_process_overflow_irq: vfe 1 overflowmask 10,bus_error 3f9f

[ 69.584186] msm_vfe47_axi_halt: VFE1 halt for recovery, blocking 0

[ 69.591502] overflow processed

[ 69.629538] msm_isp_axi_halt: VFE1 Bus overflow detected: start recovery!

[ 69.647575] msm_vfe47_axi_halt: VFE1 halt for recovery, blocking 1

[ 69.714162] ispif_process_irq: PIX0 frame id: 3

[ 69.747542] ispif_process_irq: PIX0 frame id: 4

[ 69.747636] msm_isp_process_overflow_irq: vfe 1 overflowmask 10,bus_error 3f9f

[ 69.750957] msm_vfe47_axi_halt: VFE1 halt for recovery, blocking 0

[ 69.758259] overflow processed

[ 72.052223] msm_private_ioctl:Notifying subdevs about potential sof freeze

[ 72.052397] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR0 = 0x0

[ 72.058063] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR1 = 0x1

[ 72.063528] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR2 = 0x0

[ 72.068912] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR3 = 0x20

[ 72.074288] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR4 = 0x0

[ 72.079667] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR5 = 0x0

[ 72.080922] ispif_process_irq: PIX0 frame id: 74

[ 72.090512] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR6 = 0x4

[ 72.095207] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR7 = 0x0

[ 72.100500] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR8 = 0x80

[ 72.105885] msm_csiphy_irq CSIPHY0_IRQ_STATUS_ADDR9 = 0x40

[ 72.111752] msm_csid_irq CSID0_IRQ_STATUS_ADDR = 0xff

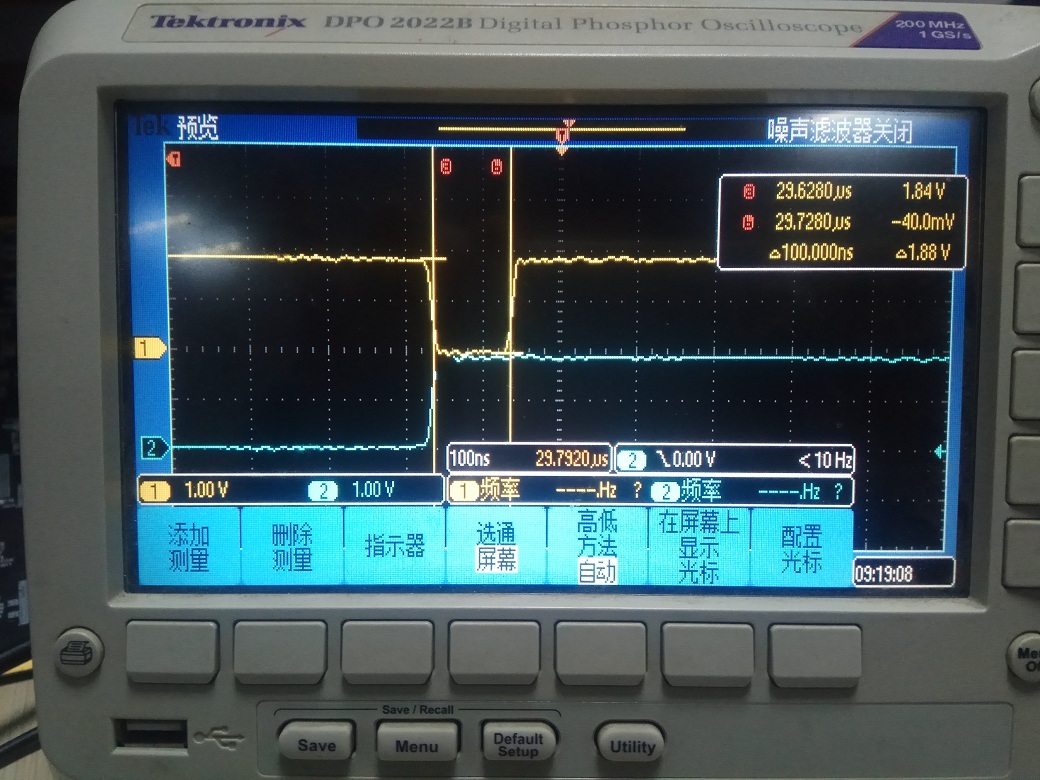

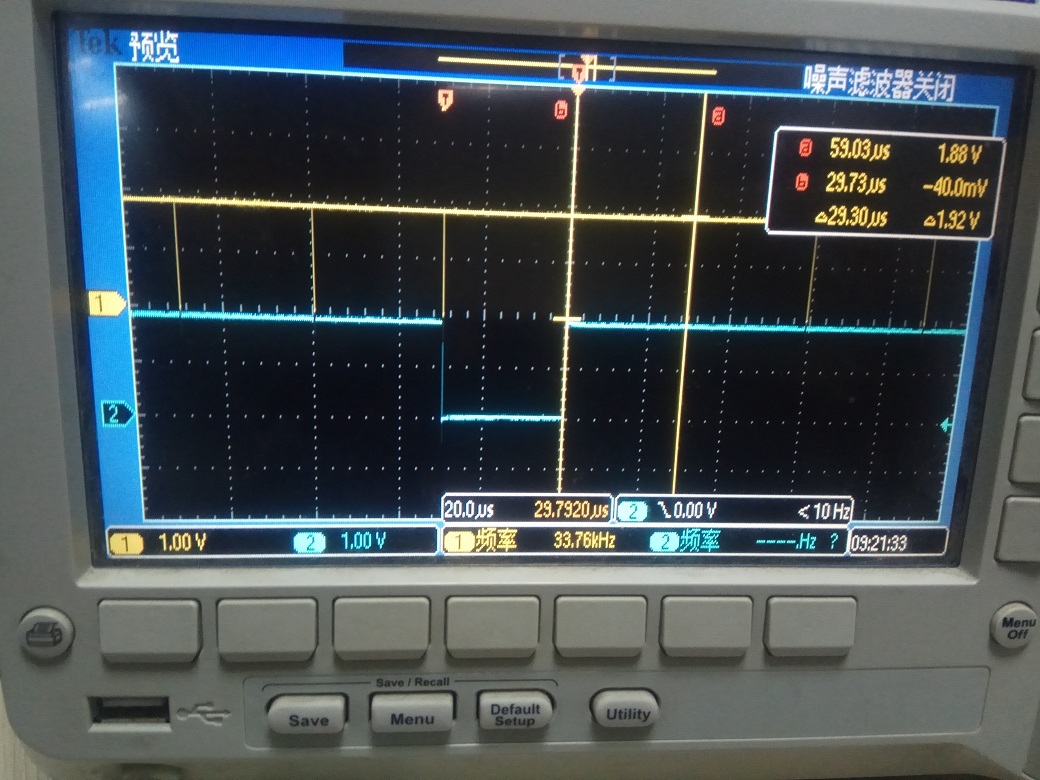

we find DS90UB954 get image size (reg 0x73-0x76) is WRONG!!!!

Can you help me to slove this problem?