Phy is connected to a ZynqMP chip. In uboot, mii dump produces:

ZynqMP> mii info c

PHY 0x0C: OUI = 0x80028, Model = 0x23, Rev = 0x01, 10baseT, HDX

ZynqMP> mii dump c 0

0. (1140) -- PHY control register --

(8000:0000) 0.15 = 0 reset

(4000:0000) 0.14 = 0 loopback

(2040:0040) 0. 6,13 = b10 speed selection = 1000 Mbps

(1000:1000) 0.12 = 1 A/N enable

(0800:0000) 0.11 = 0 power-down

(0400:0000) 0.10 = 0 isolate

(0200:0000) 0. 9 = 0 restart A/N

(0100:0100) 0. 8 = 1 duplex = full

(0080:0000) 0. 7 = 0 collision test enable

(003f:0000) 0. 5- 0 = 0 (reserved)

ZynqMP> mii dump c 1

1. (7949) -- PHY status register --

(8000:0000) 1.15 = 0 100BASE-T4 able

(4000:4000) 1.14 = 1 100BASE-X full duplex able

(2000:2000) 1.13 = 1 100BASE-X half duplex able

(1000:1000) 1.12 = 1 10 Mbps full duplex able

(0800:0800) 1.11 = 1 10 Mbps half duplex able

(0400:0000) 1.10 = 0 100BASE-T2 full duplex able

(0200:0000) 1. 9 = 0 100BASE-T2 half duplex able

(0100:0100) 1. 8 = 1 extended status

(0080:0000) 1. 7 = 0 (reserved)

(0040:0040) 1. 6 = 1 MF preamble suppression

(0020:0000) 1. 5 = 0 A/N complete

(0010:0000) 1. 4 = 0 remote fault

(0008:0008) 1. 3 = 1 A/N able

(0004:0000) 1. 2 = 0 link status

(0002:0000) 1. 1 = 0 jabber detect

(0001:0001) 1. 0 = 1 extended capabilities

ZynqMP> mii dump c 2

2. (2000) -- PHY ID 1 register --

(ffff:2000) 2.15- 0 = 8192 OUI portion

ZynqMP> mii dump c 3

3. (a231) -- PHY ID 2 register --

(fc00:a000) 3.15-10 = 40 OUI portion

(03f0:0230) 3. 9- 4 = 35 manufacturer part number

(000f:0001) 3. 3- 0 = 1 manufacturer rev. number

ZynqMP> mii dump c 4

4. (01e1) -- Autonegotiation advertisement register --

(8000:0000) 4.15 = 0 next page able

(4000:0000) 4.14 = 0 (reserved)

(2000:0000) 4.13 = 0 remote fault

(1000:0000) 4.12 = 0 (reserved)

(0800:0000) 4.11 = 0 asymmetric pause

(0400:0000) 4.10 = 0 pause enable

(0200:0000) 4. 9 = 0 100BASE-T4 able

(0100:0100) 4. 8 = 1 100BASE-TX full duplex able

(0080:0080) 4. 7 = 1 100BASE-TX able

(0040:0040) 4. 6 = 1 10BASE-T full duplex able

(0020:0020) 4. 5 = 1 10BASE-T able

(001f:0001) 4. 4- 0 = 1 selector = IEEE 802.3

ZynqMP> mii dump c 5

5. (0000) -- Autonegotiation partner abilities register --

(8000:0000) 5.15 = 0 next page able

(4000:0000) 5.14 = 0 acknowledge

(2000:0000) 5.13 = 0 remote fault

(1000:0000) 5.12 = 0 (reserved)

(0800:0000) 5.11 = 0 asymmetric pause able

(0400:0000) 5.10 = 0 pause able

(0200:0000) 5. 9 = 0 100BASE-T4 able

(0100:0000) 5. 8 = 0 100BASE-X full duplex able

(0080:0000) 5. 7 = 0 100BASE-TX able

(0040:0000) 5. 6 = 0 10BASE-T full duplex able

(0020:0000) 5. 5 = 0 10BASE-T able

(001f:0000) 5. 4- 0 = 0 selector = ???

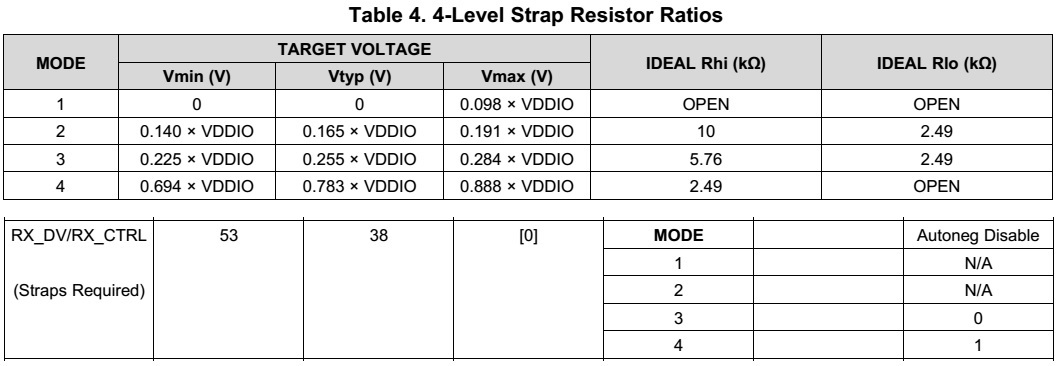

Cannot get the chip to auto negotiate at all. Several cables, routers, and laptops tested.

Tried to force A/N with mii write c 0 0x1340 with no luck.

Is there something i can probe or check to debug this?