Part Number: SN65DSI84-Q1

Other Parts Discussed in Thread: SN65DSI84, DSI-TUNER

Hi team,

I have some questions on SN65DSI84-Q1 application.

We use this chip to convert the DSI interface of Qualcomm 820A output to a dual LVDS interface (1920x1080 resolution)

If there is a register configuration reference code for this chip, please provide us with a reference.

We design the circuit with reference to EVM board.

The connection of the circuit is basically the same, but the difference lies in the configuration of resistance and capacitance parameters.

Please help confirm the following questions:

1. VCC power consumption problem; the specification has an example. 400*900 resolution output, the maximum power consumption is 164mA.

Our resolution is 1920*1080. What is the maximum power consumption? Is there any reference in this respect?

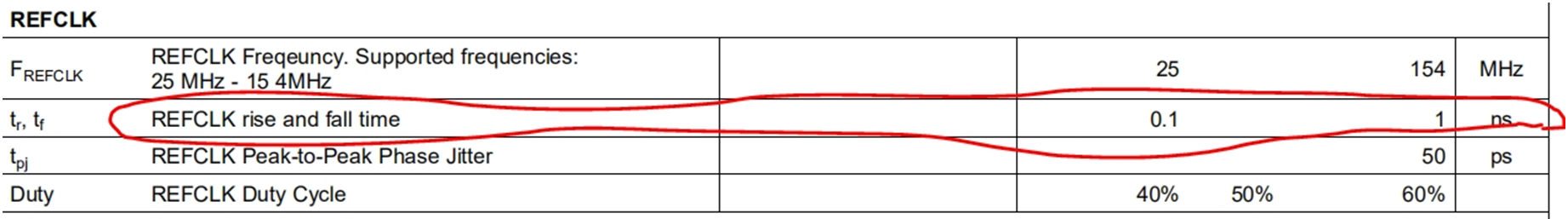

2.REFCLK, recommended on EVM is 25-154 Mhz clock.

We use 25 MHz active crystal oscillator.There is a time requirement for rise/fall in specifications.

Is this 20%-80% VCC time or 30%-70% VCC time?

3. Are there any initialization codes for SN65DSI84 adapted to 1920*1080 resolution for reference?

thanks.